# EnergySmart: Toward Energy-Efficient Many-Cores for Near-Threshold Computing

**Ulya R. Karpuzcu**, Abhishek Sinkar\*, Nam Sung Kim\*, Josep Torrellas\* University of Minnesota \*University of Illinois \*University of Wisconsin

University of Minnesota

Power x Energy efficiency = Performance

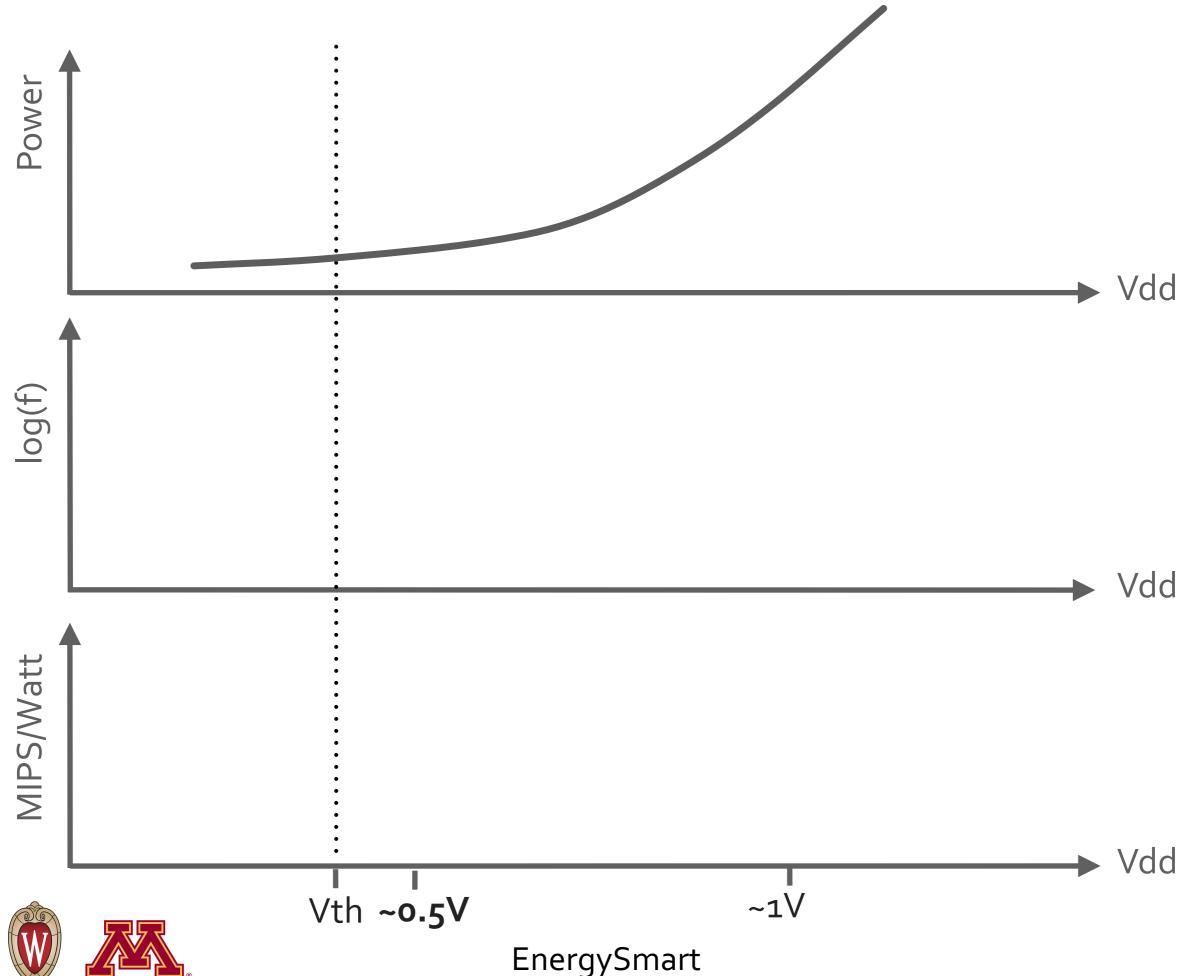

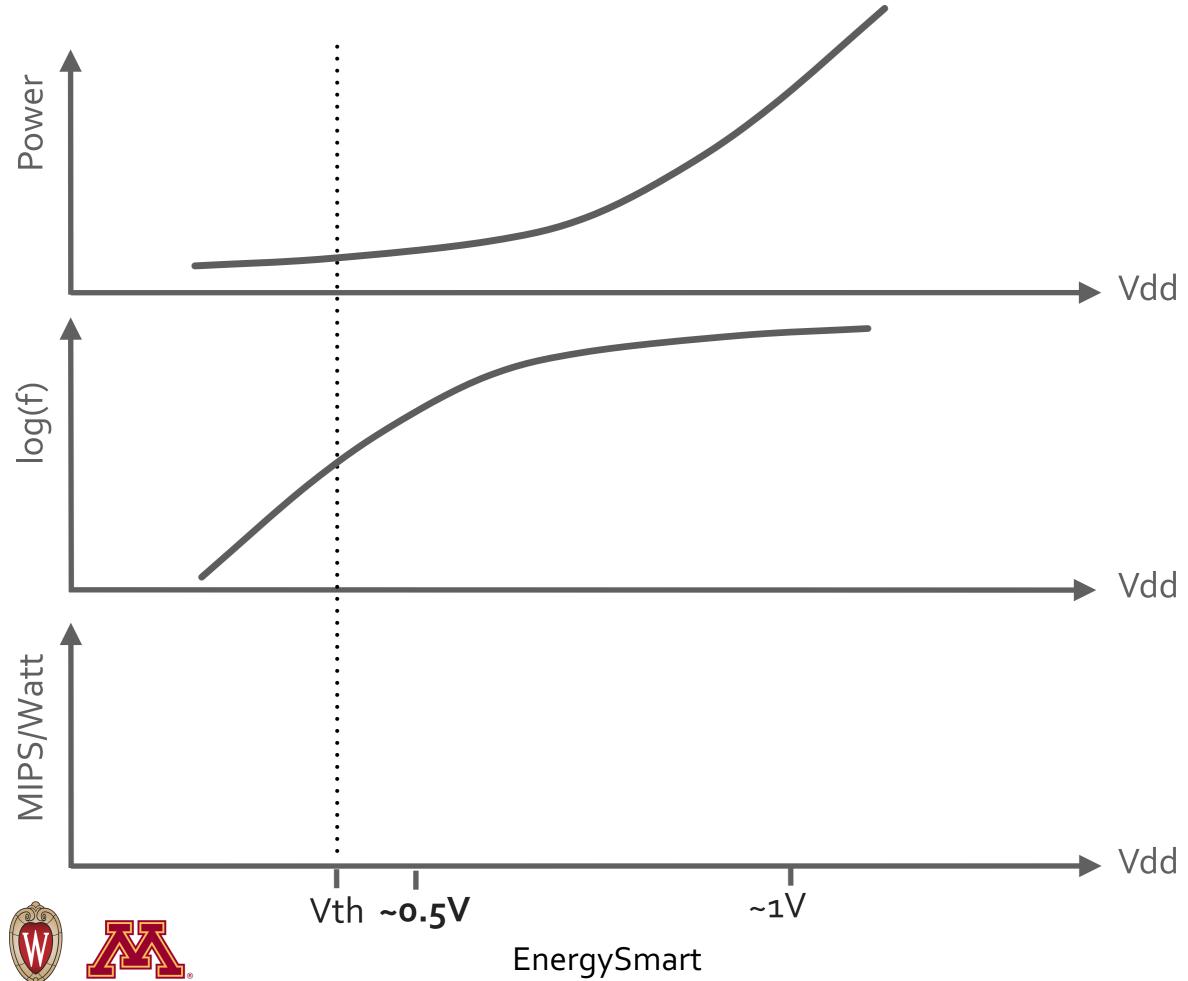

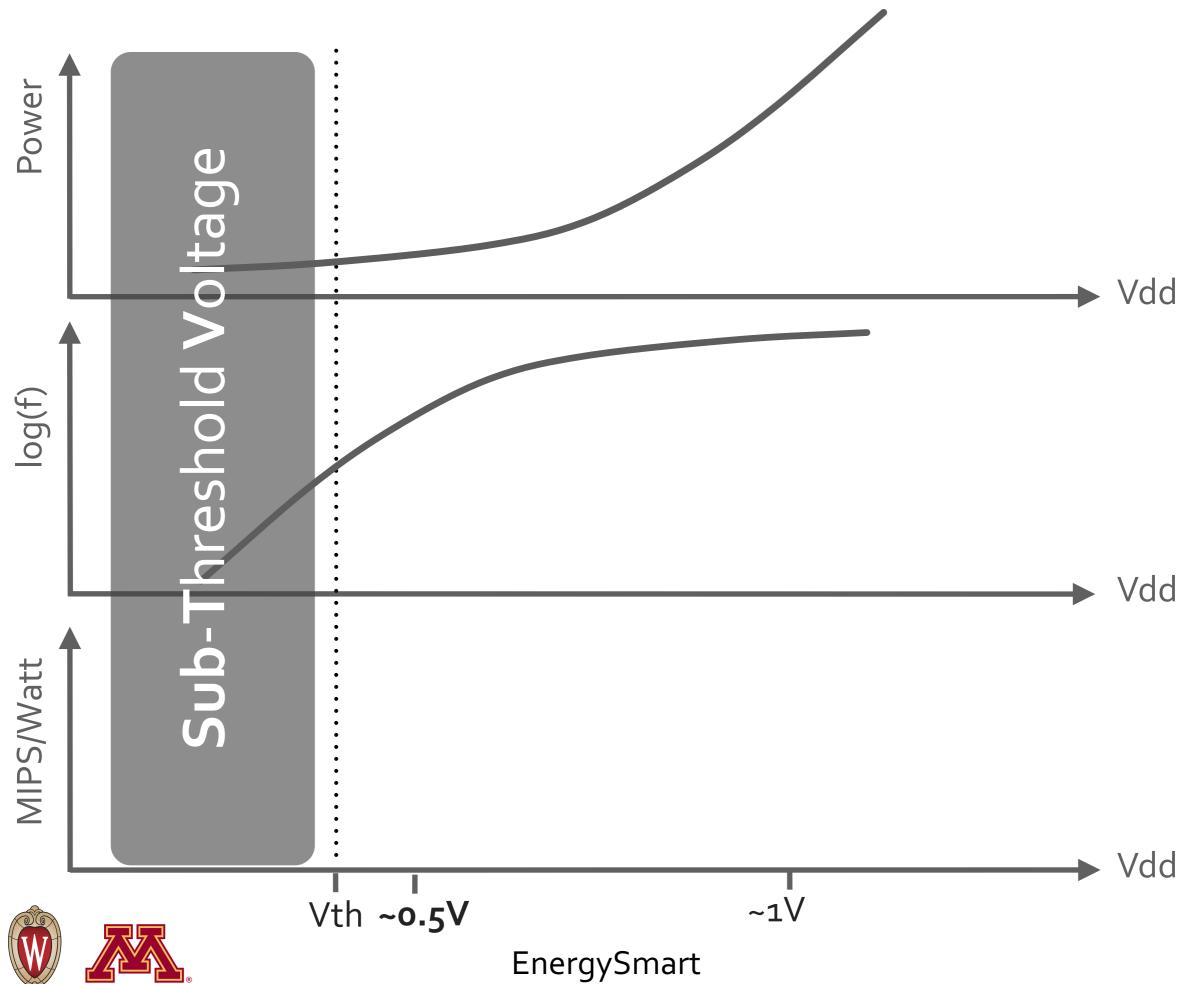

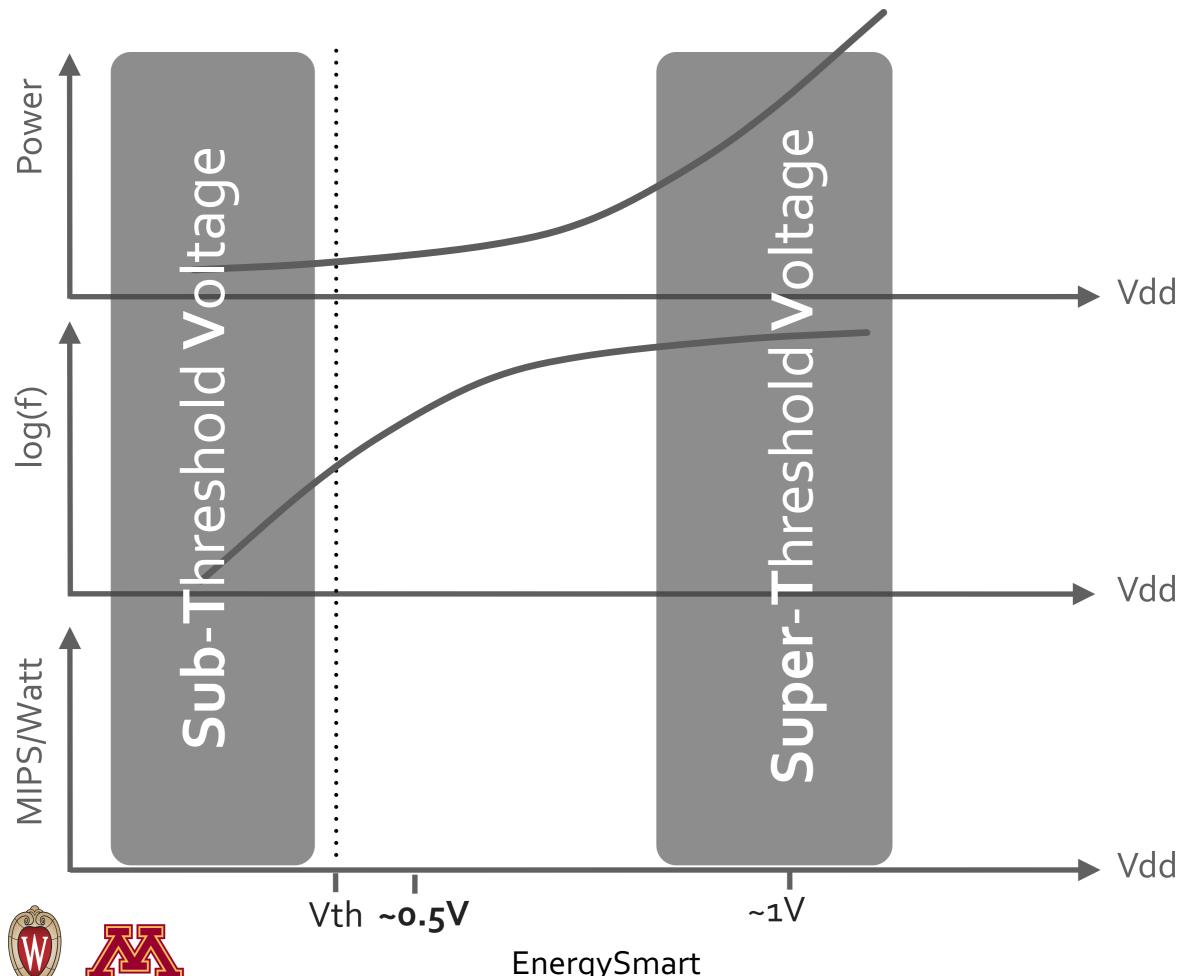

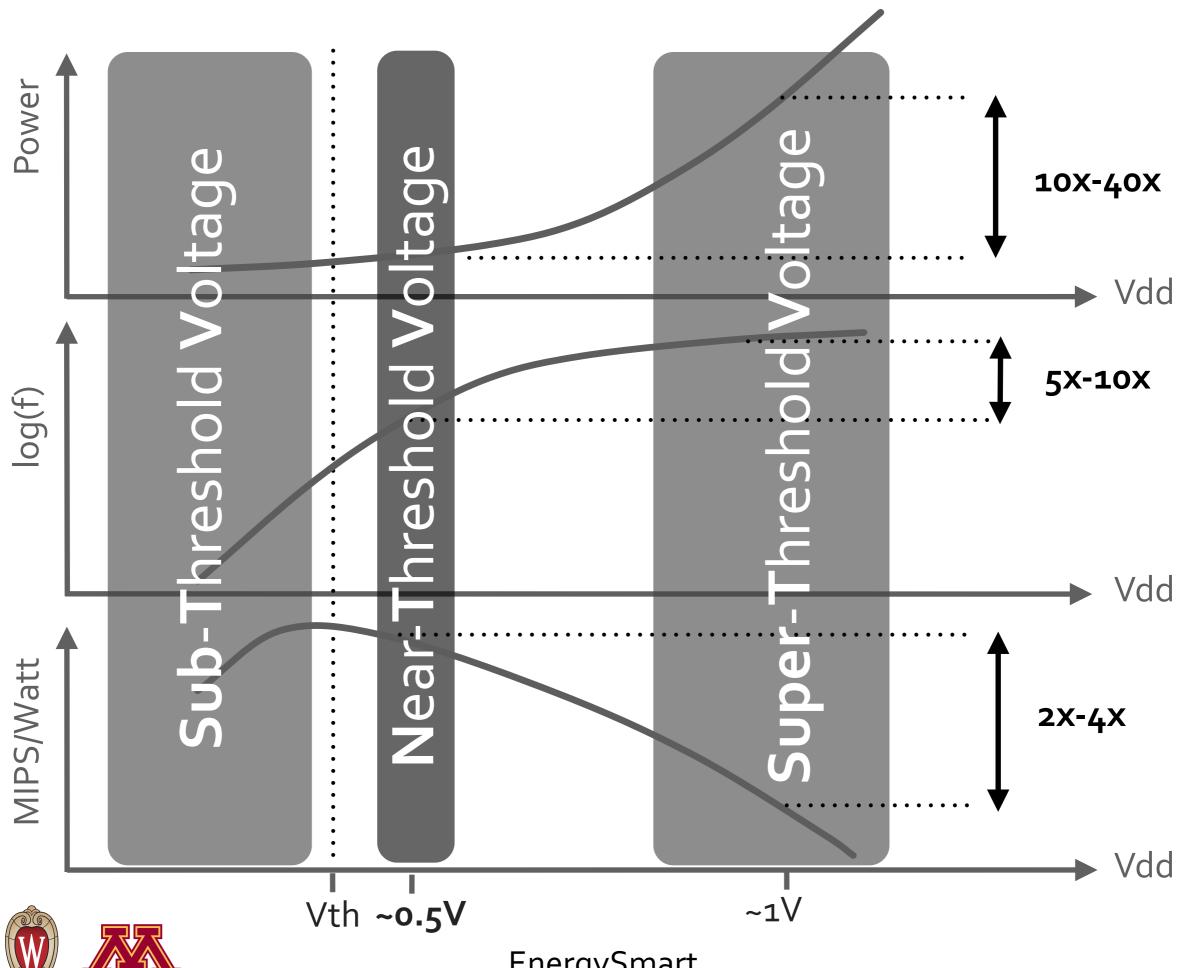

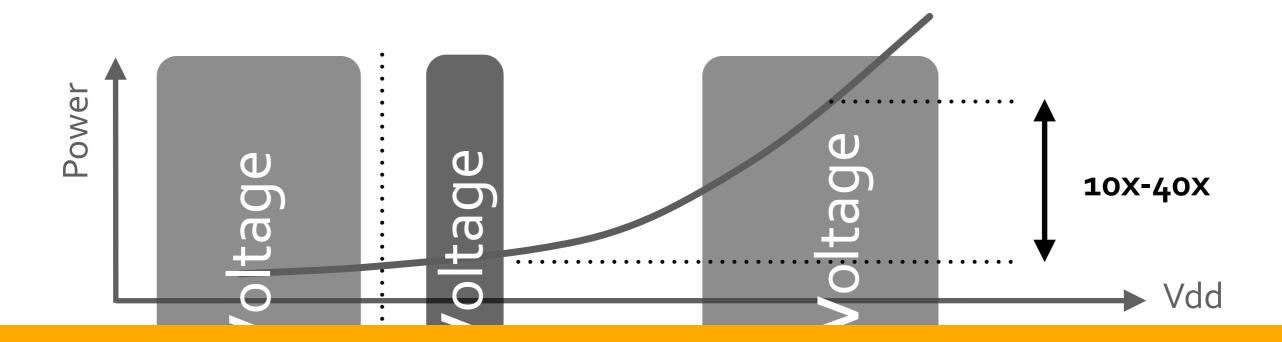

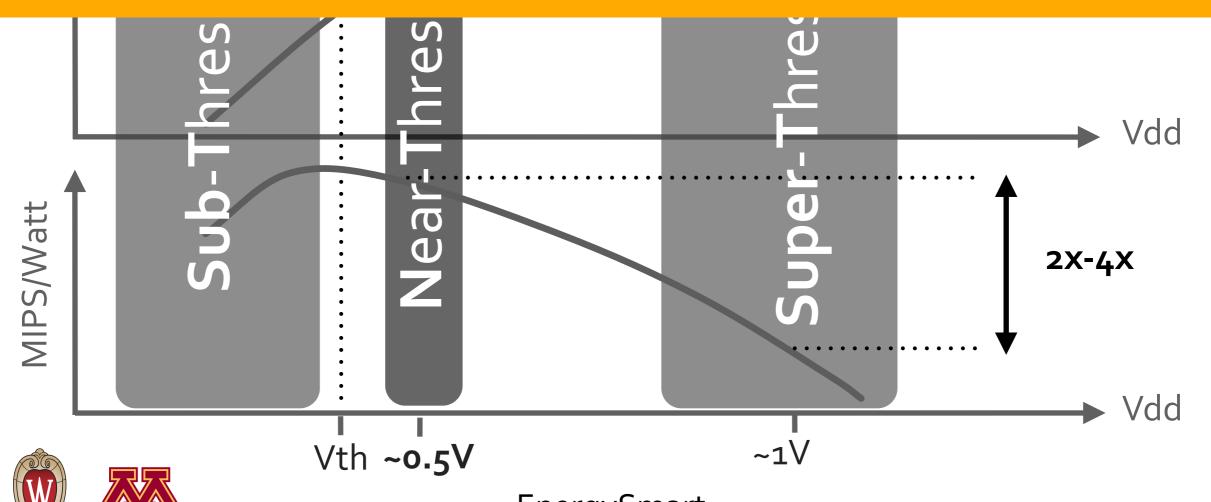

Vdd scaling increases energy-efficiency

- Vdd scaling increases energy-efficiency

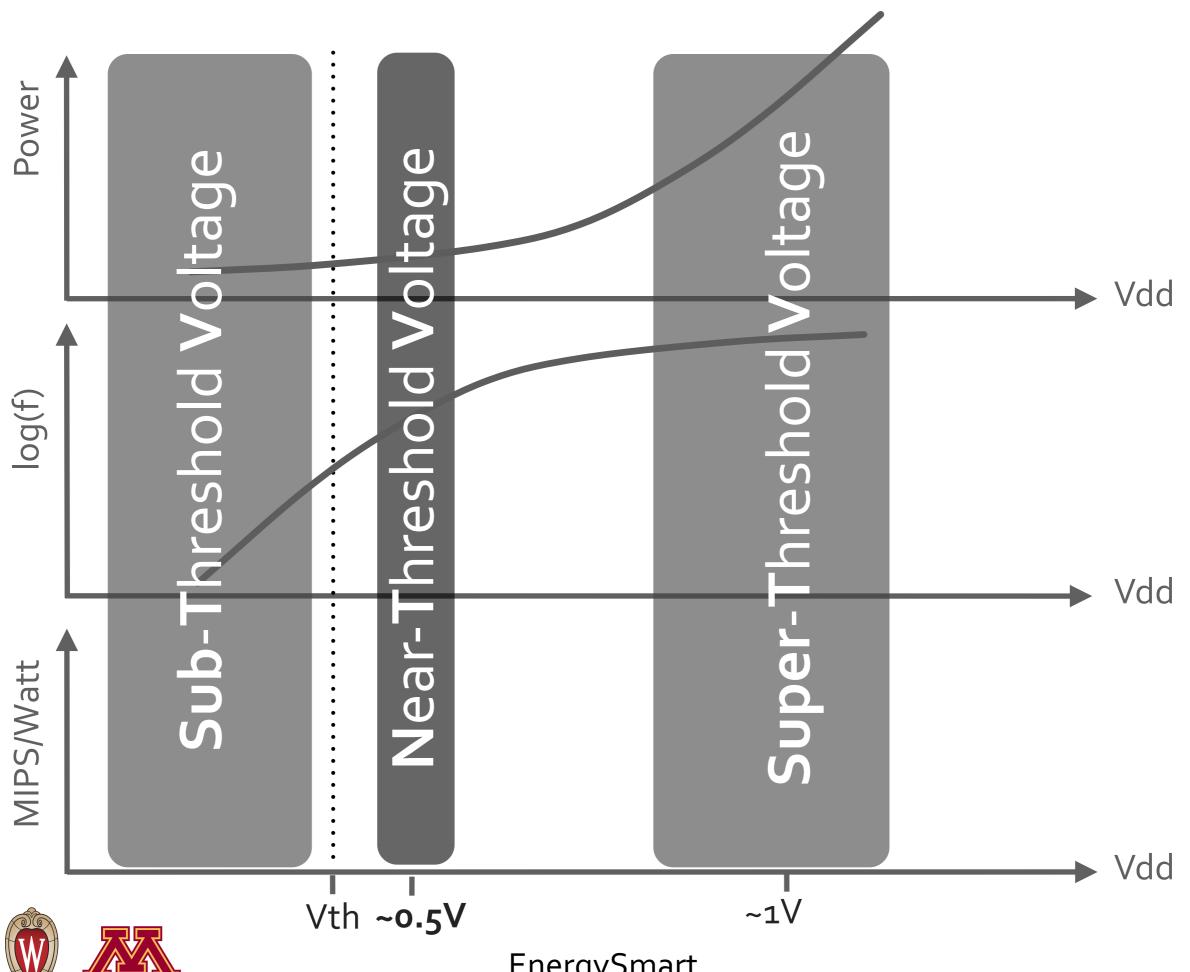

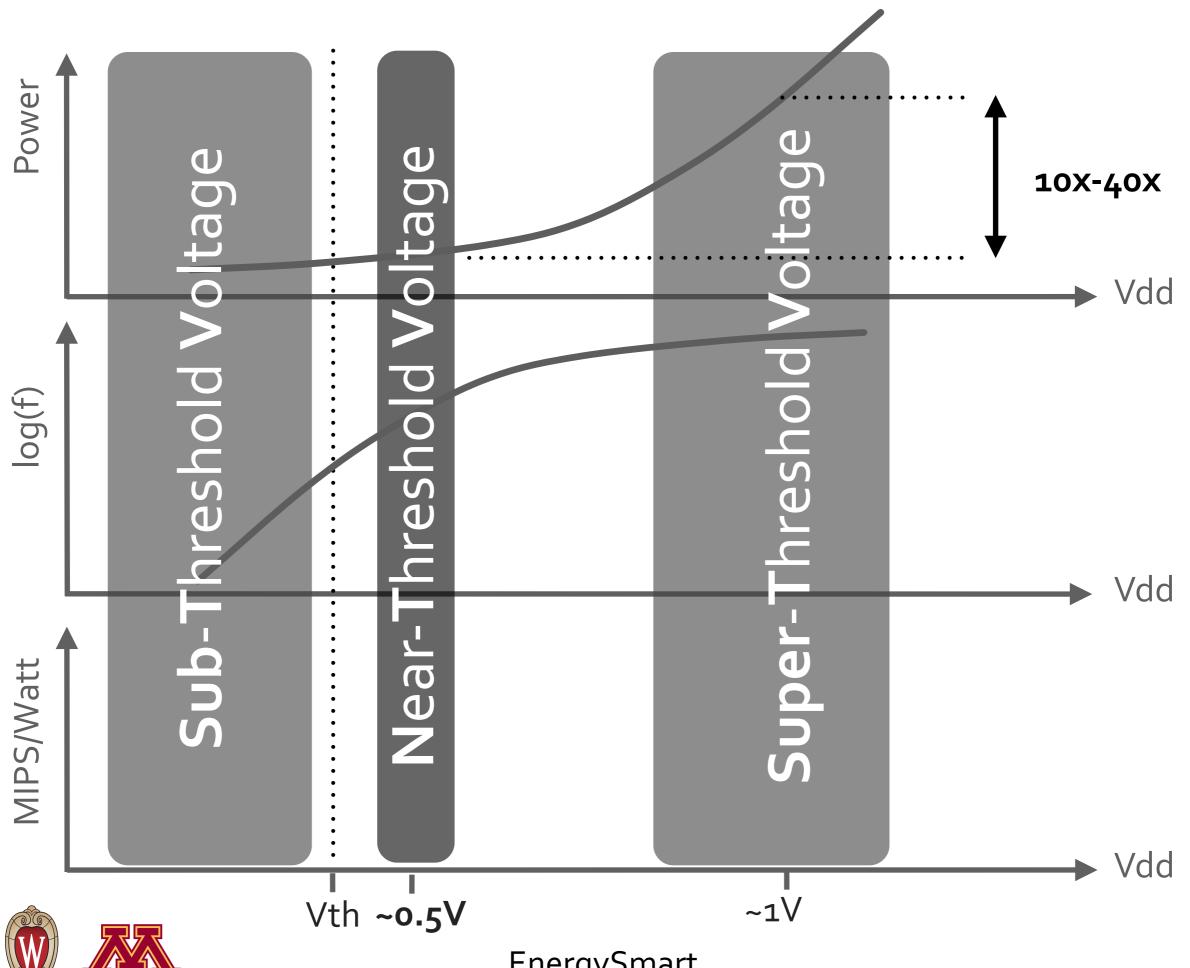

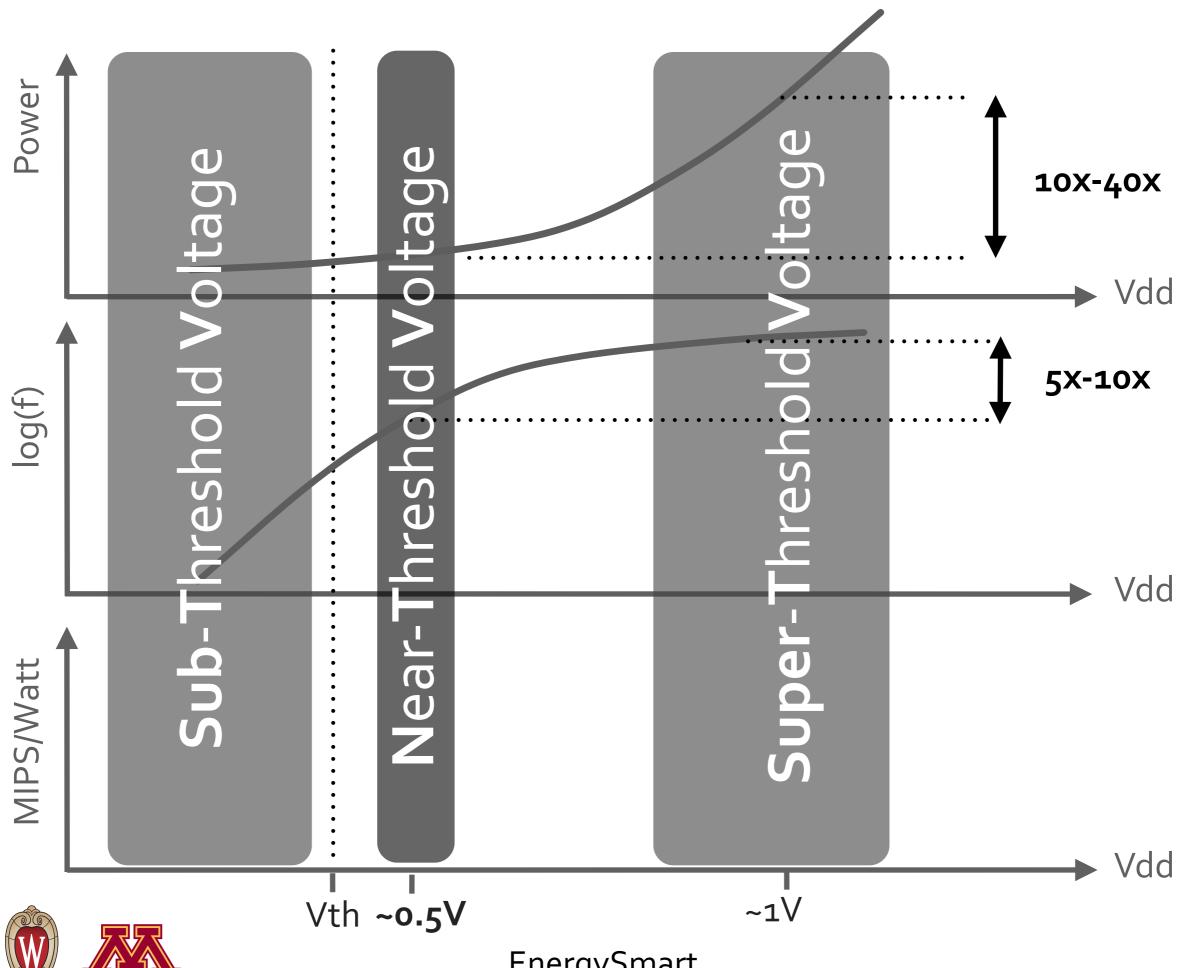

- Near-Threshold Voltage -- NTV Operation

- Vdd scaling increases energy-efficiency

- Near-Threshold Voltage -- NTV Operation

- Vdd reduces to slightly above Vth: ~0.5V

Power x Energy efficiency = Performance

- Vdd scaling increases energy-efficiency

- Near-Threshold Voltage -- NTV Operation

- Vdd reduces to slightly above Vth: ~0.5V

- vs. 1V for conventional or Super-threshold voltage -- STV

- Vdd scaling increases energy-efficiency

- Near-Threshold Voltage -- NTV Operation

- Vdd reduces to slightly above Vth: ~0.5V

- vs. 1V for conventional or Super-threshold voltage -- STV

- Drawbacks

- Vdd scaling increases energy-efficiency

- Near-Threshold Voltage -- NTV Operation

- Vdd reduces to slightly above Vth: ~0.5V

- vs. 1V for conventional or Super-threshold voltage -- STV

- Drawbacks

- Lower f: Need more parallelism > large chips

- Vdd scaling increases energy-efficiency

- Near-Threshold Voltage -- NTV Operation

- Vdd reduces to slightly above Vth: ~0.5V

- vs. 1V for conventional or Super-threshold voltage -- STV

- Drawbacks

- Lower f: Need more parallelism > large chips

- Higher impact of variation

Conventional techniques to tolerate variation are not cost-effective at NTV

- Conventional techniques to tolerate variation are not cost-effective at NTV

- Support for multiple on-chip Vdd domains hurts energy-efficiency

- Conventional techniques to tolerate variation are not cost-effective at NTV

- Support for multiple on-chip Vdd domains hurts energy-efficiency

- Propose EnergySmart organization to maximize energy-efficiency at NTV

- Conventional techniques to tolerate variation are not cost-effective at NTV

- Support for multiple on-chip Vdd domains hurts energy-efficiency

- Propose EnergySmart organization to maximize energy-efficiency at NTV

- Single Vdd domain, multiple f domains

- Conventional techniques to tolerate variation are not cost-effective at NTV

- Support for multiple on-chip Vdd domains hurts energy-efficiency

- Propose EnergySmart organization to maximize energy-efficiency at NTV

- Single Vdd domain, multiple f domains

- Simple hardware

- Conventional techniques to tolerate variation are not cost-effective at NTV

- Support for multiple on-chip Vdd domains hurts energy-efficiency

- Propose EnergySmart organization to maximize energy-efficiency at NTV

- Single Vdd domain, multiple f domains

- Simple hardware

- Smart, variation-aware core assignment

- Conventional techniques to tolerate variation are not cost-effective at NTV

- Support for multiple on-chip Vdd domains hurts energy-efficiency

- Propose EnergySmart organization to maximize energy-efficiency at NTV

- Single Vdd domain, multiple f domains

- Simple hardware

- Smart, variation-aware core assignment

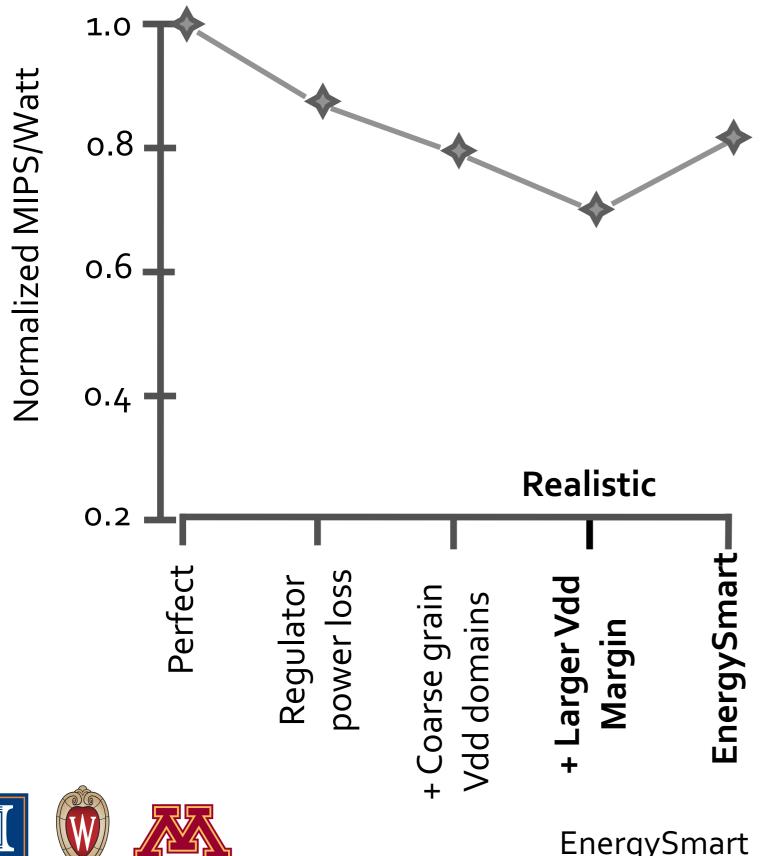

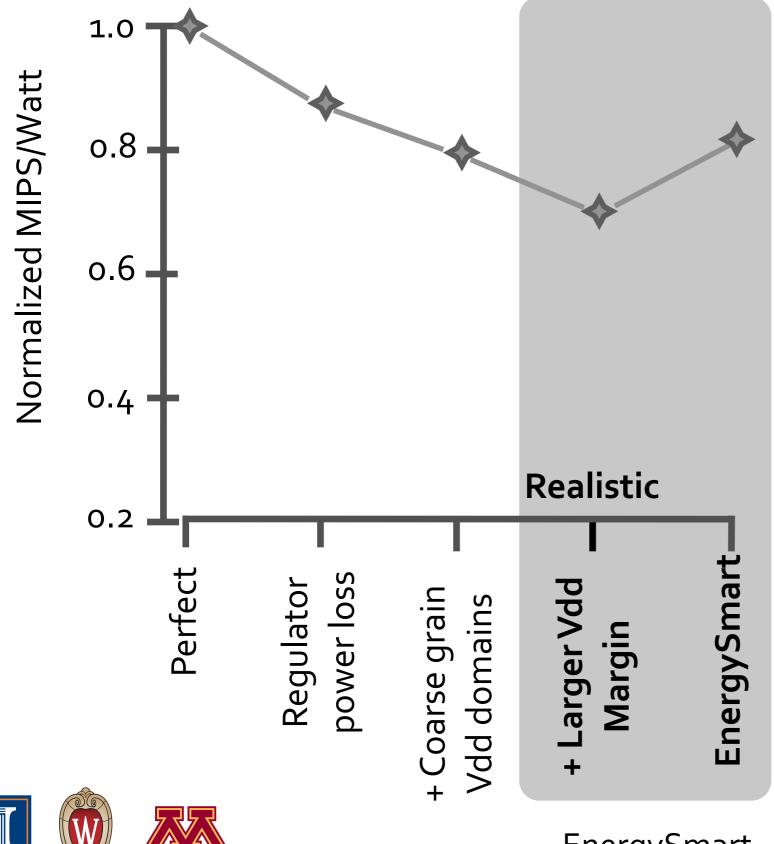

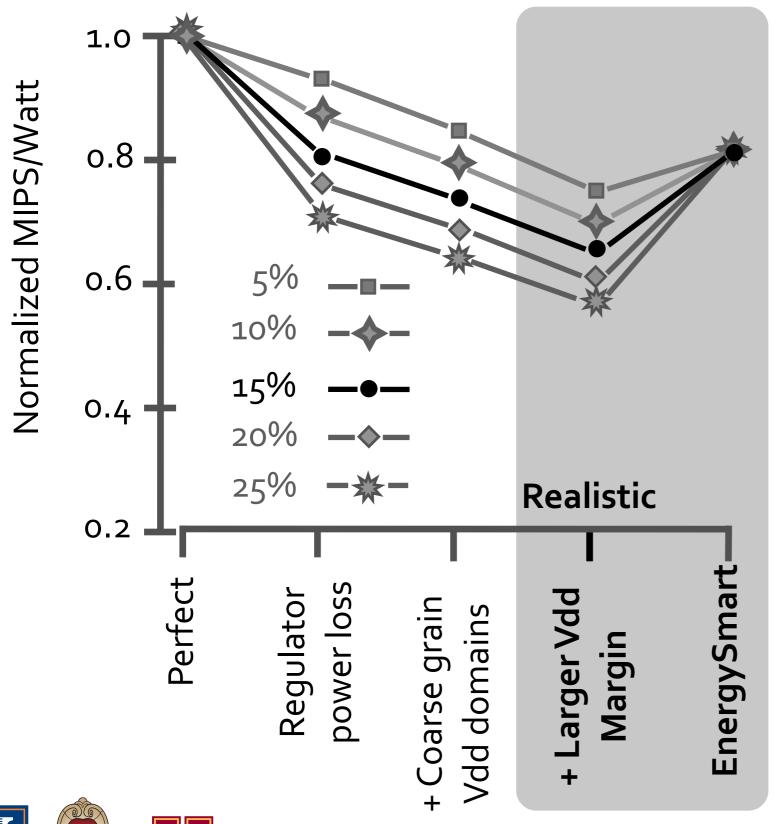

- Energy-efficiency within 81% of perfect organization (as opposed to 69% for conventional)

#### At NTV, more cores can be active than at STV

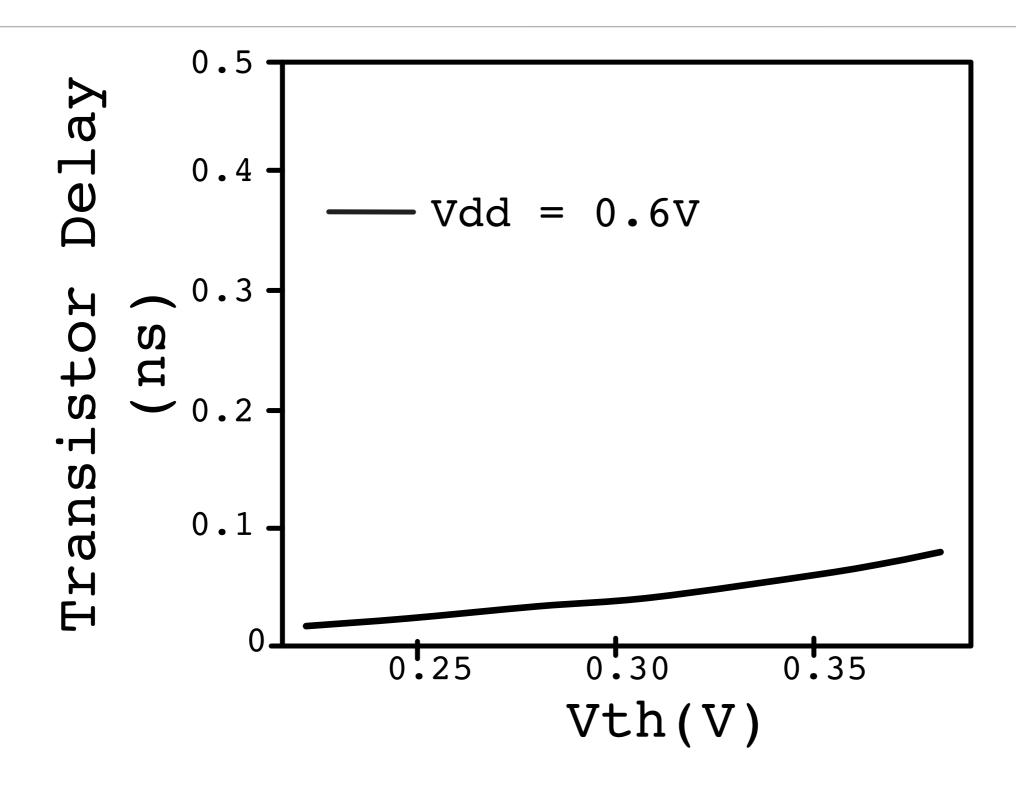

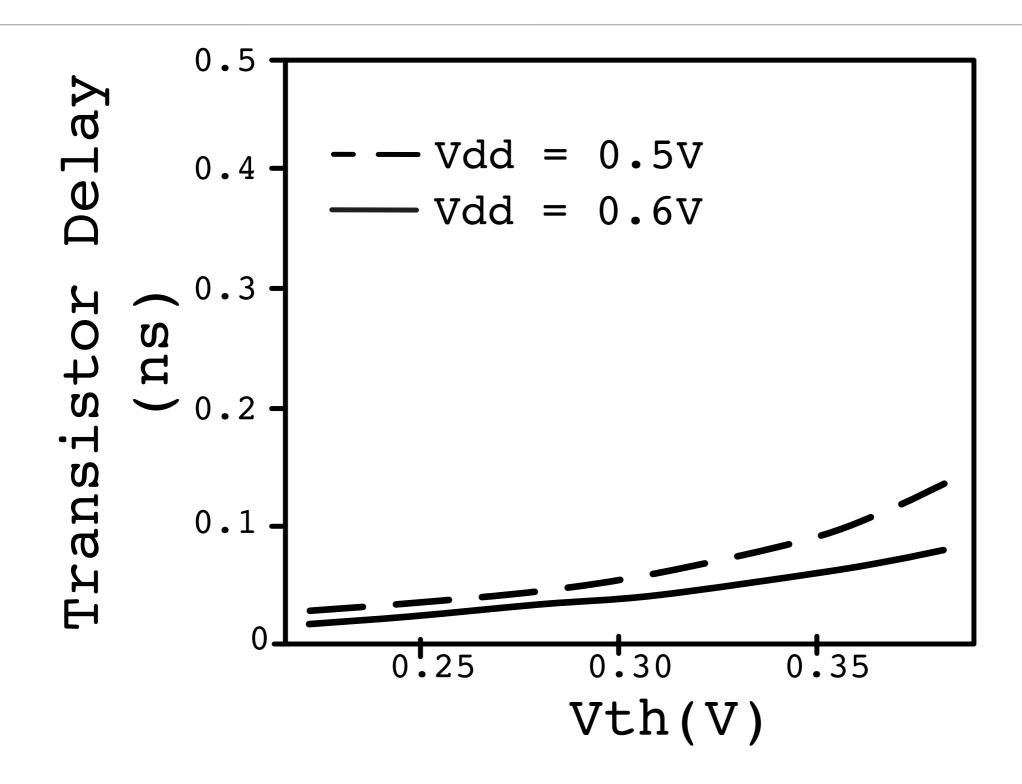

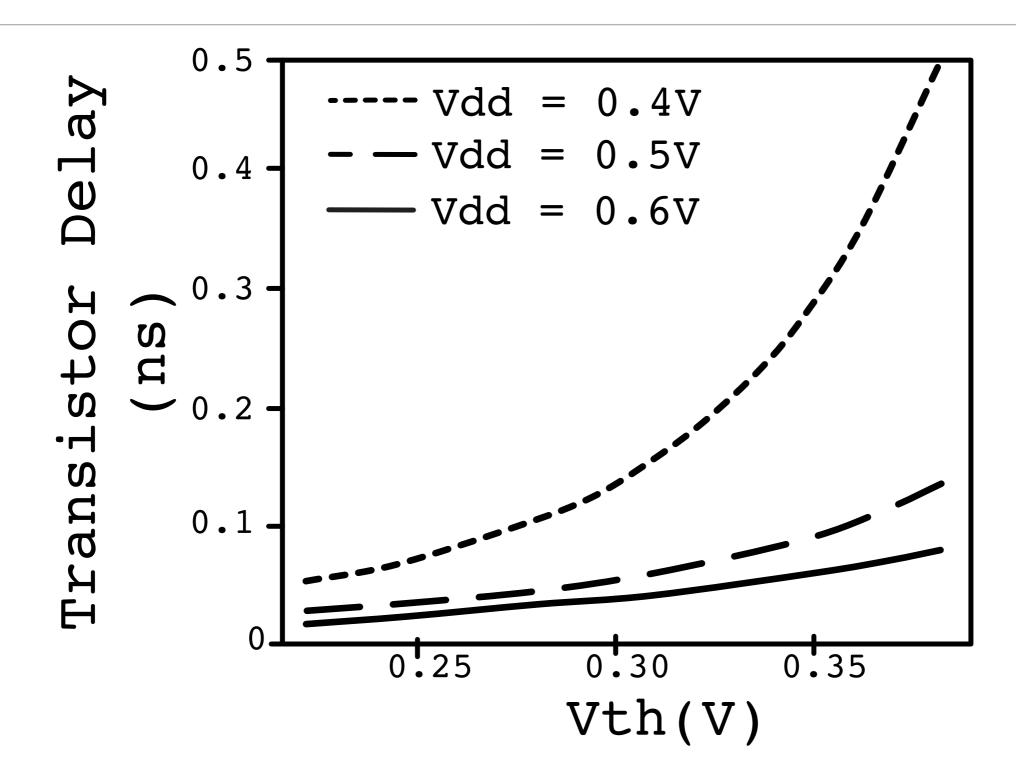

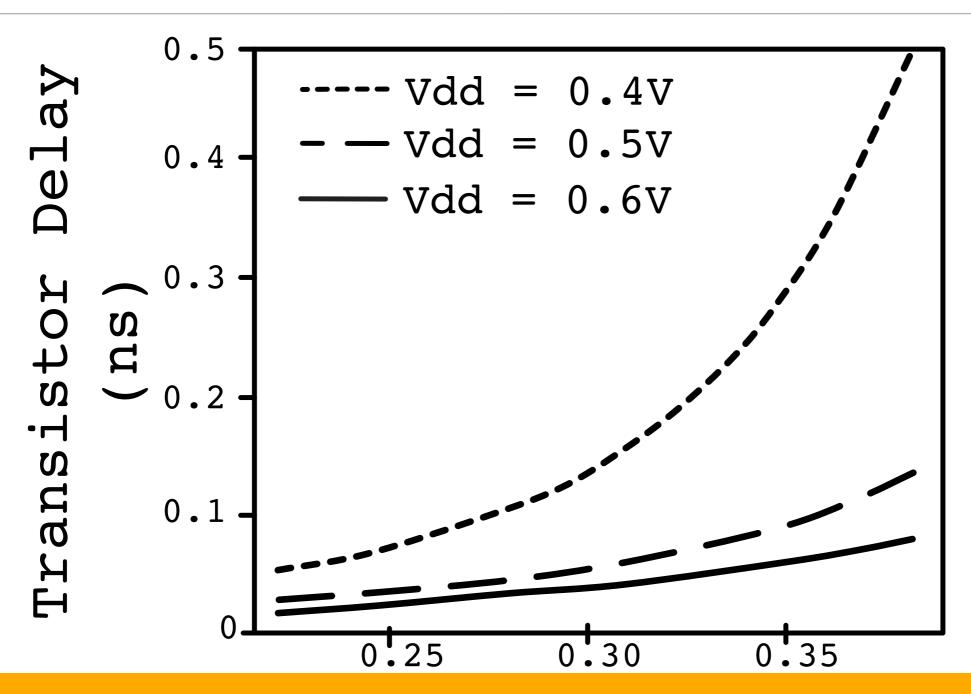

Same \( \Delta V\) th causes higher f variation at NTV than at STV

Attack source of variation

adapt Vth

- Attack source of variation

adapt Vth

- Adaptive Body Biasing

- Attack source of variation

adapt Vth

- Adaptive Body Biasing

- Questionable for new device architectures

- Attack source of variation

adapt Vth

- Adaptive Body Biasing

- Questionable for new device architectures

- Attack effect of variation adapt Vdd

- Attack source of variation

adapt Vth

- Adaptive Body Biasing

- Questionable for new device architectures

- Attack effect of variation

adapt Vdd

- Adaptive Supply Voltage, Dynamic Voltage Scaling

- Attack source of variation

adapt Vth

- Adaptive Body Biasing

- Questionable for new device architectures

- Attack effect of variation

adapt Vdd

- Adaptive Supply Voltage, Dynamic Voltage Scaling

- Effectiveness increases with multiple voltage domains

- Attack source of variation

adapt Vth

- Adaptive Body Biasing

- Questionable for new device architectures

- Attack effect of variation

adapt Vdd

- Adaptive Supply Voltage, Dynamic Voltage Scaling

- Effectiveness increases with multiple voltage domains

- Cost-effective?

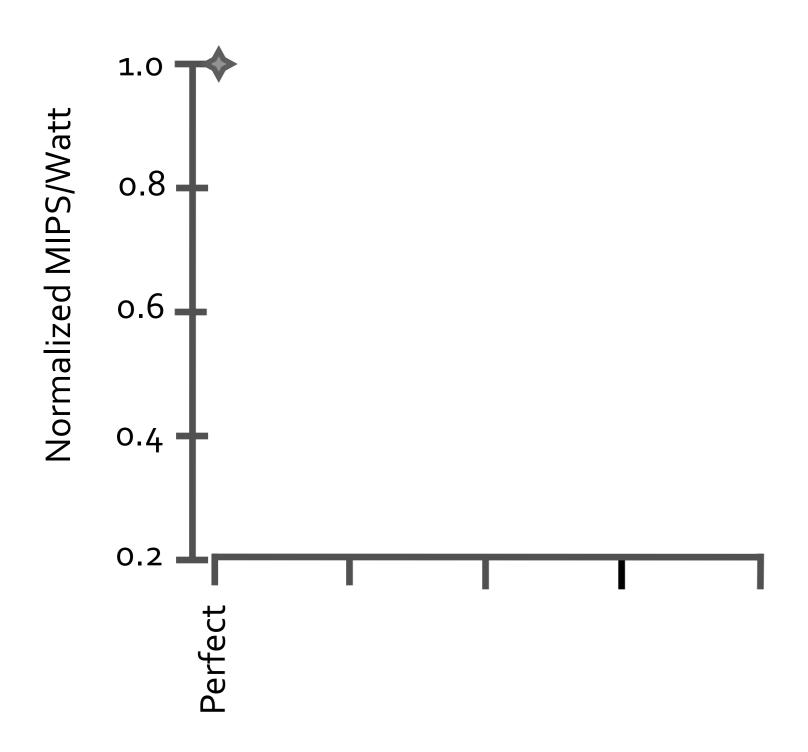

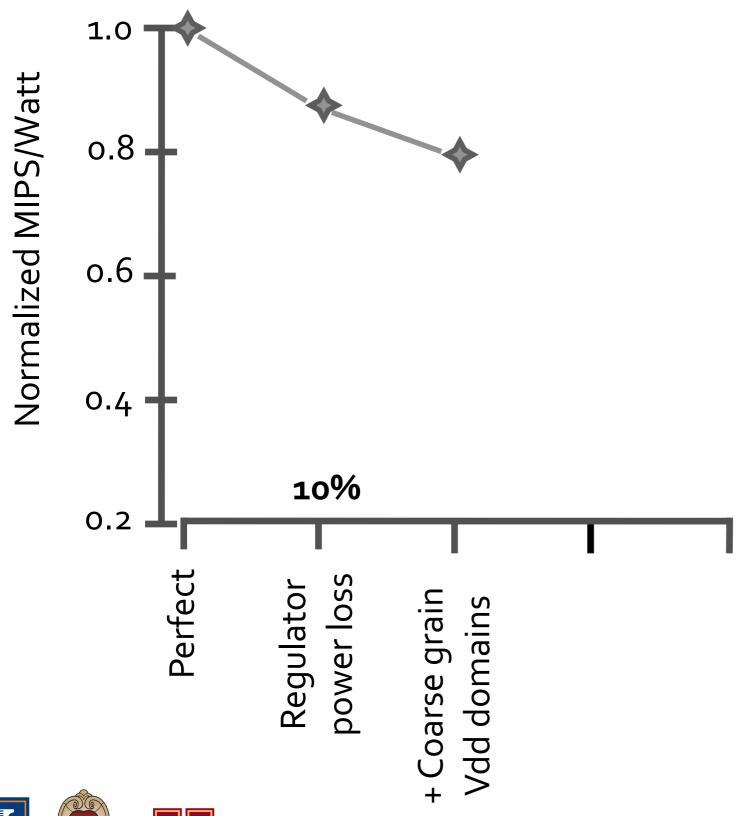

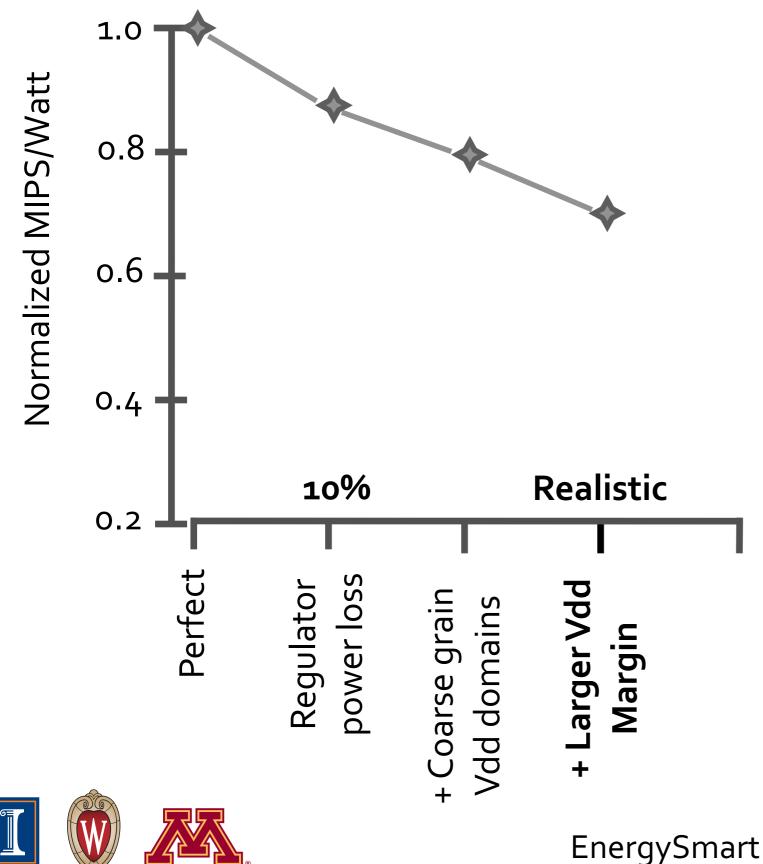

(I) On chip regulators' high power loss

- (I) On chip regulators' high power loss

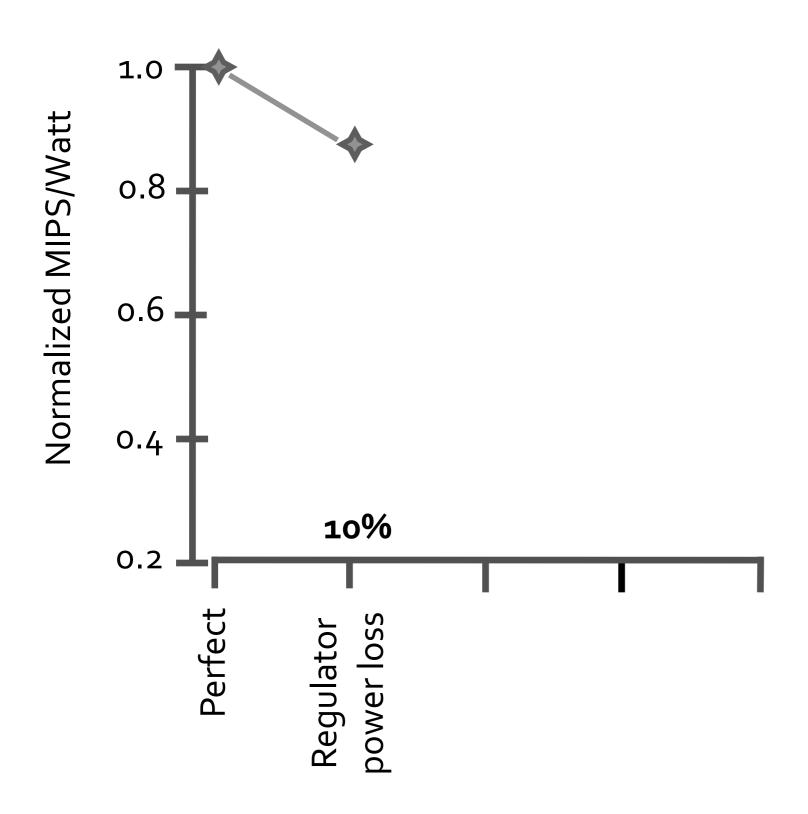

- 10% power loss or more

### (I) On chip regulators' high power loss

- 10% power loss or more

- Barely any loss is acceptable at energy-conscious NTV

- (I) On chip regulators' high power loss

- 10% power loss or more

- Barely any loss is acceptable at energy-conscious NTV

- (II) Vdd domain granularity (# of cores per domain)

- (I) On chip regulators' high power loss

- 10% power loss or more

- Barely any loss is acceptable at energy-conscious NTV

- (II) Vdd domain granularity (# of cores per domain)

- Fine: Effective tuning but expensive due to large #cores

### (I) On chip regulators' high power loss

- 10% power loss or more

- Barely any loss is acceptable at energy-conscious NTV

- (II) Vdd domain granularity (# of cores per domain)

- Fine: Effective tuning but expensive due to large #cores

- Coarse: More practical, yet suffers from variation inside

### (I) On chip regulators' high power loss

- 10% power loss or more

- Barely any loss is acceptable at energy-conscious NTV

- (II) Vdd domain granularity (# of cores per domain)

- Fine: Effective tuning but expensive due to large #cores

- Coarse: More practical, yet suffers from variation inside

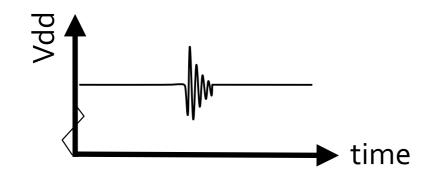

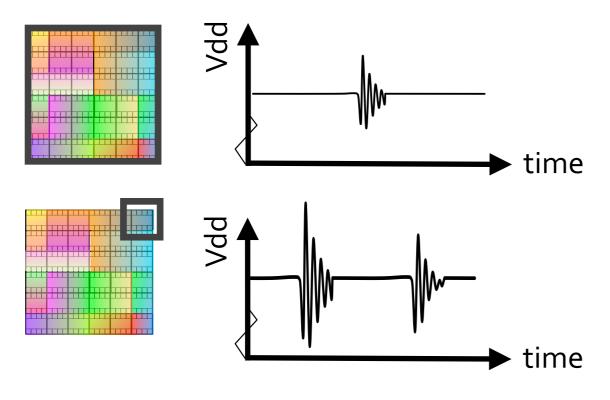

### (III) Vdd noise

### (I) On chip regulators' high power loss

- 10% power loss or more

- Barely any loss is acceptable at energy-conscious NTV

- (II) Vdd domain granularity (# of cores per domain)

- Fine: Effective tuning but expensive due to large #cores

- Coarse: More practical, yet suffers from variation inside

### (III) Vdd noise

Large domain

Averaging effects in the current drawn

### (I) On chip regulators' high power loss

- 10% power loss or more

- Barely any loss is acceptable at energy-conscious NTV

- (II) Vdd domain granularity (# of cores per domain)

- Fine: Effective tuning but expensive due to large #cores

- Coarse: More practical, yet suffers from variation inside

### (III) Vdd noise

### Large domain

Averaging effects in the current drawn

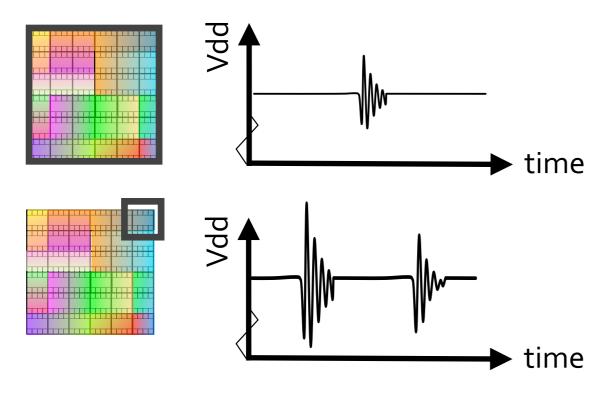

#### **Small domain**

- Less averaging ⇒ Higher Vdd droops

- Need to increase Vdd margin

### (I) On chip regulators' high power loss

10% power loss or more

### Let us keep one Vdd domain per chip. How to survive?

- Fine: Effective tuning but expensive due to large #cores

- Coarse: More practical, yet suffers from variation inside

### (III) Vdd noise

### Large domain

Averaging effects in the current drawn

#### **Small domain**

- Less averaging ⇒ Higher Vdd droops

- Need to increase Vdd margin

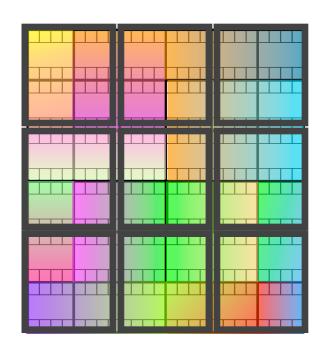

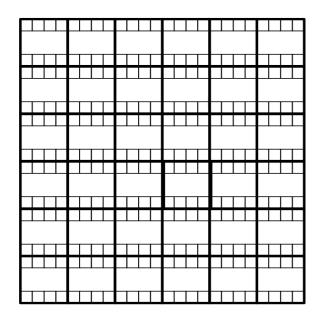

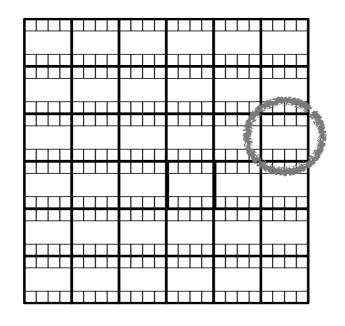

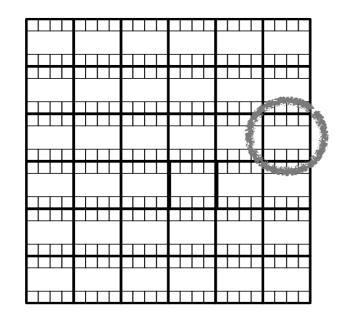

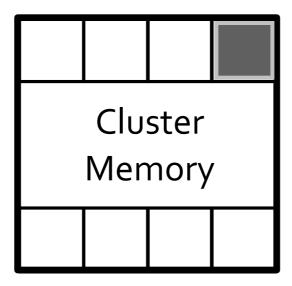

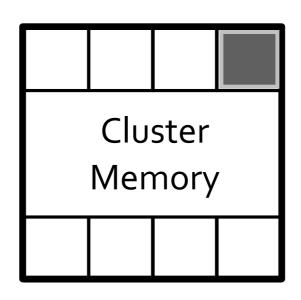

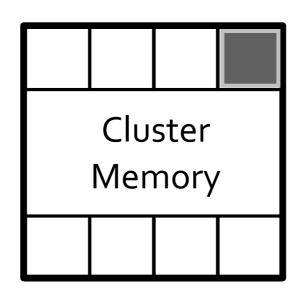

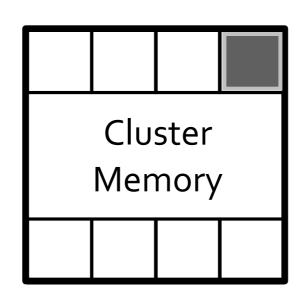

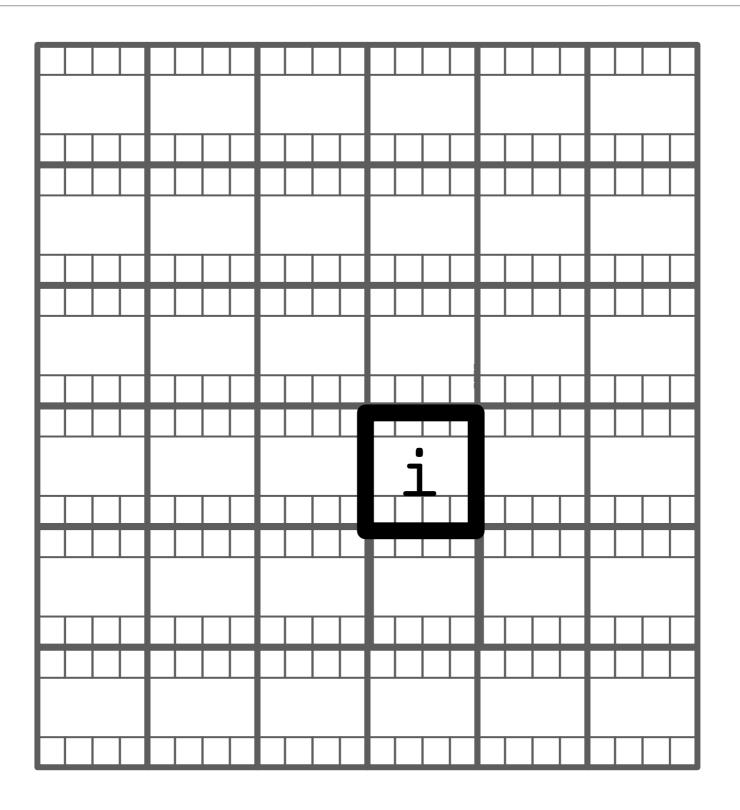

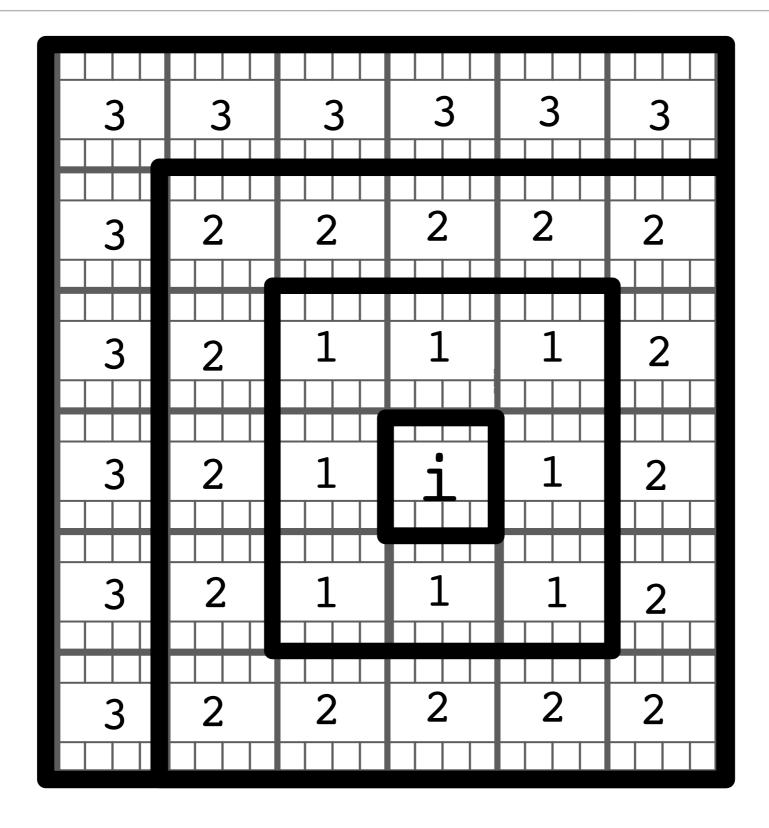

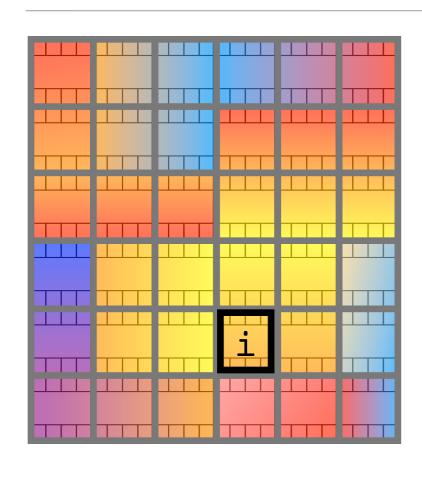

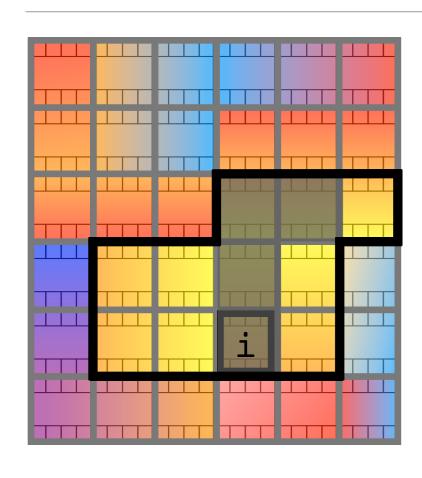

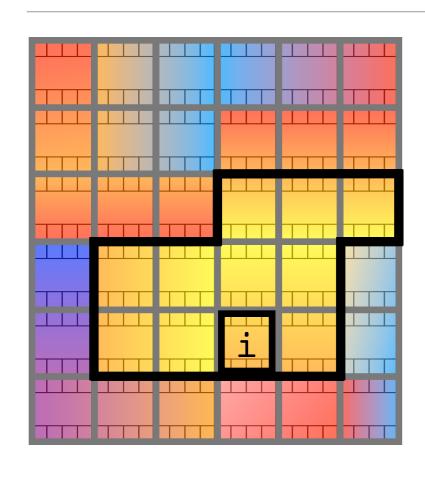

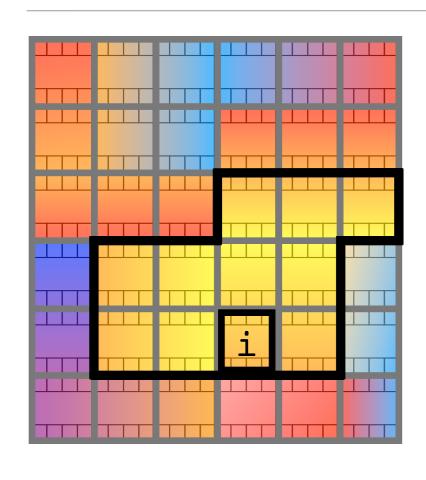

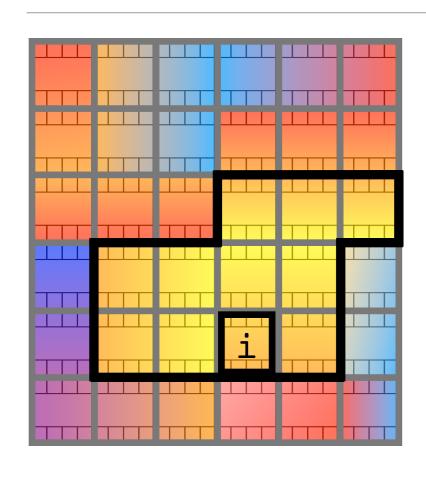

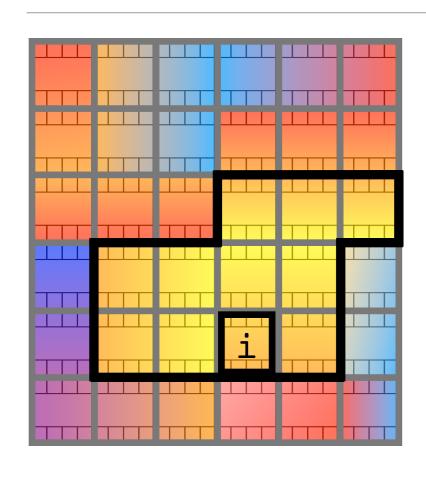

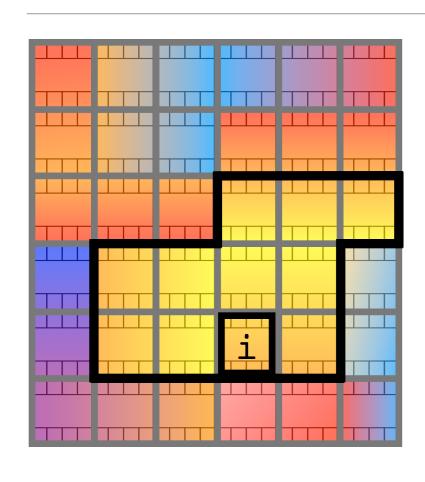

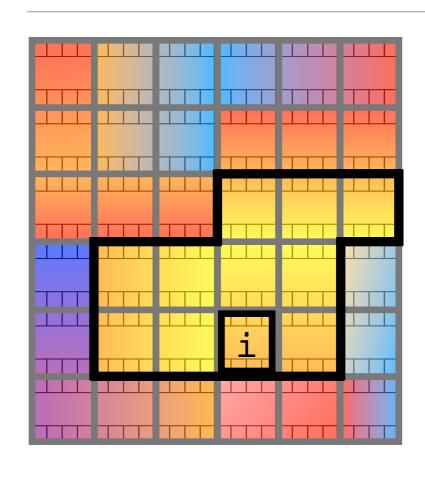

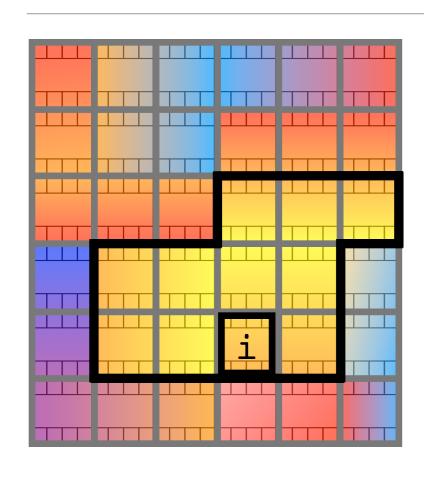

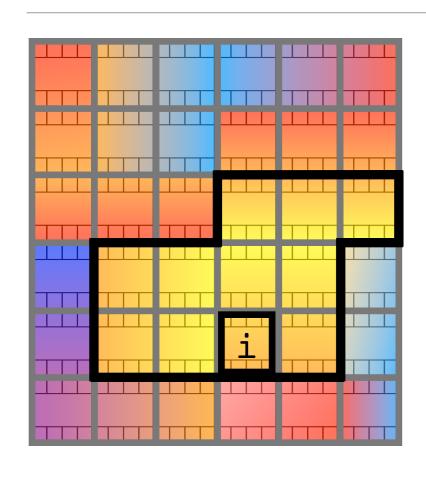

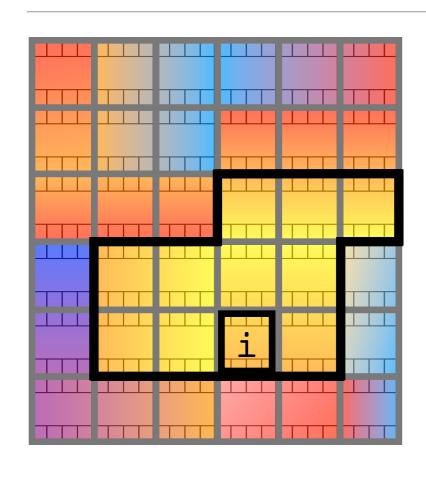

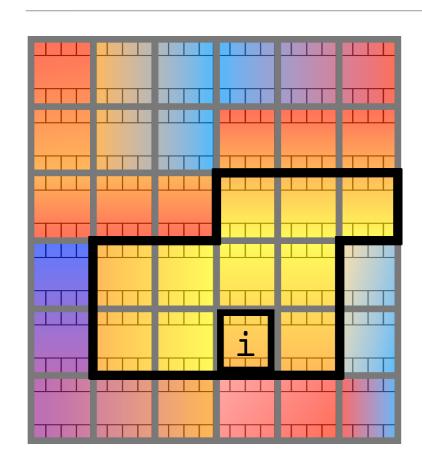

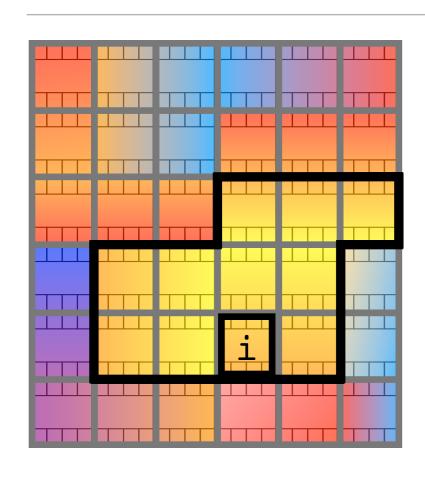

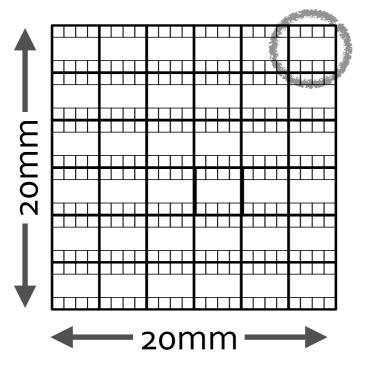

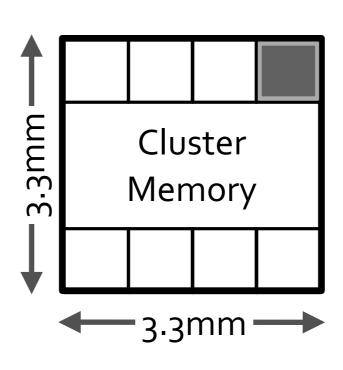

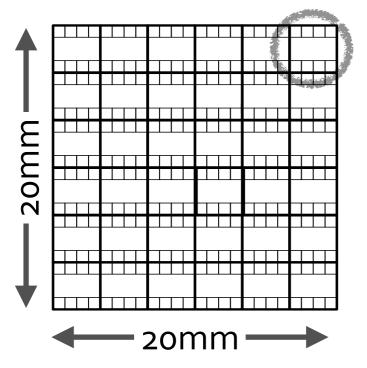

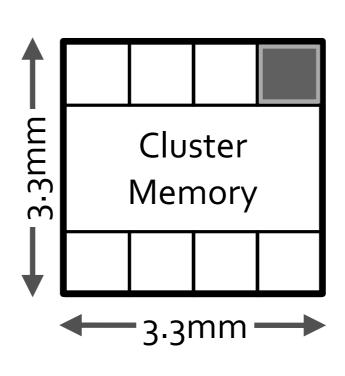

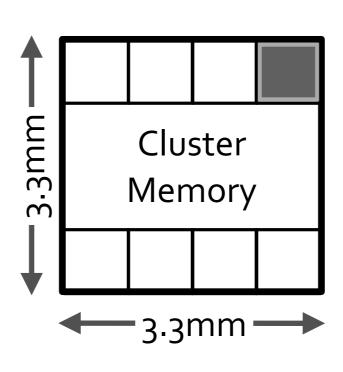

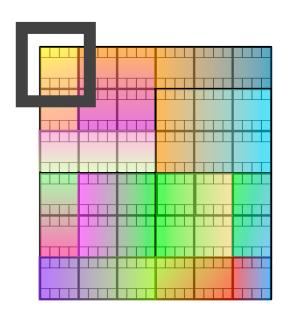

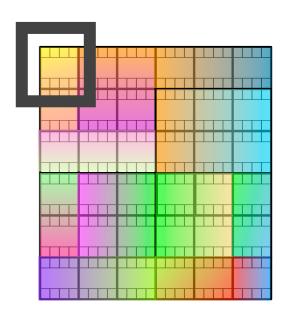

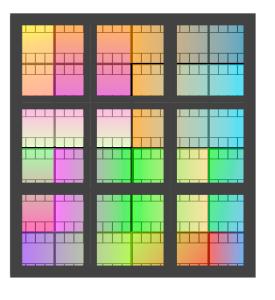

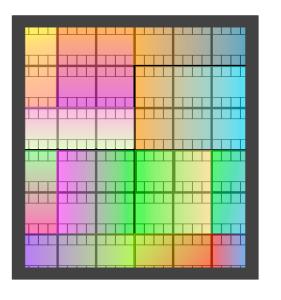

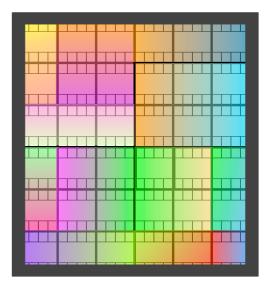

Simple, clustered hardware to exploit within-die variation

- Simple, clustered hardware to exploit within-die variation

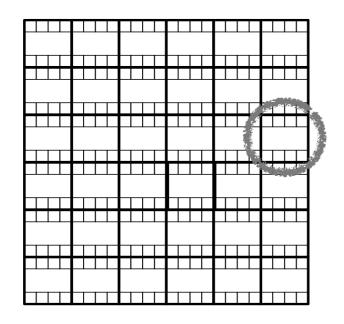

- Each cluster supports a different max f at chip-wide, single Vdd

- Simple, clustered hardware to exploit within-die variation

- Each cluster supports a different max f at chip-wide, single Vdd

Core + Local Memory

Cluster selection mimics multi-Vdd adaptation

- Simple, clustered hardware to exploit within-die variation

- Each cluster supports a different max f at chip-wide, single Vdd

- Cluster selection mimics multi-Vdd adaptation

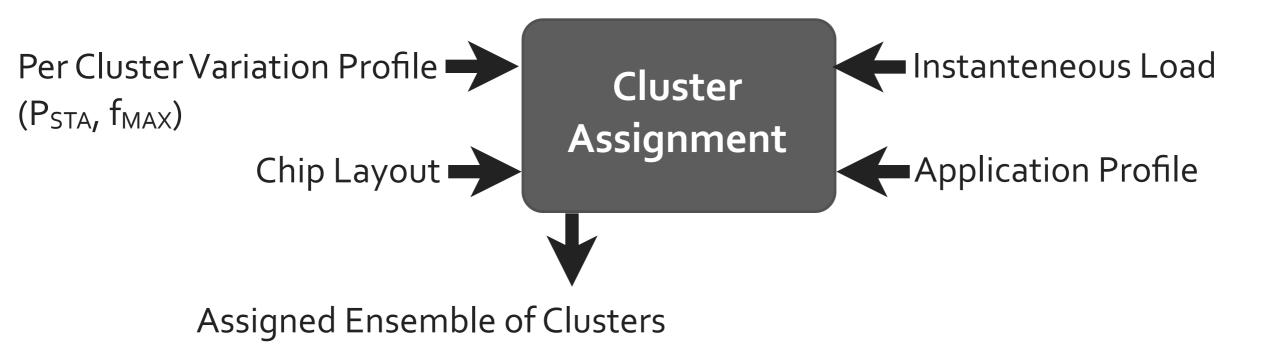

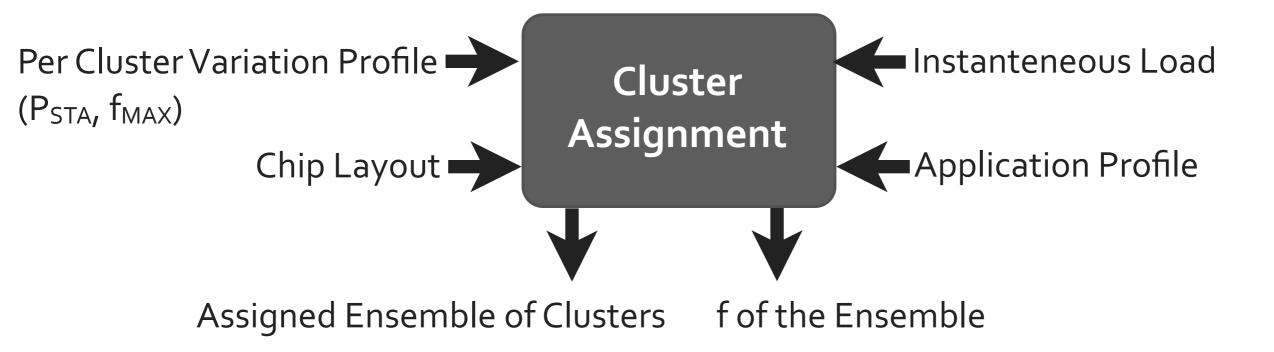

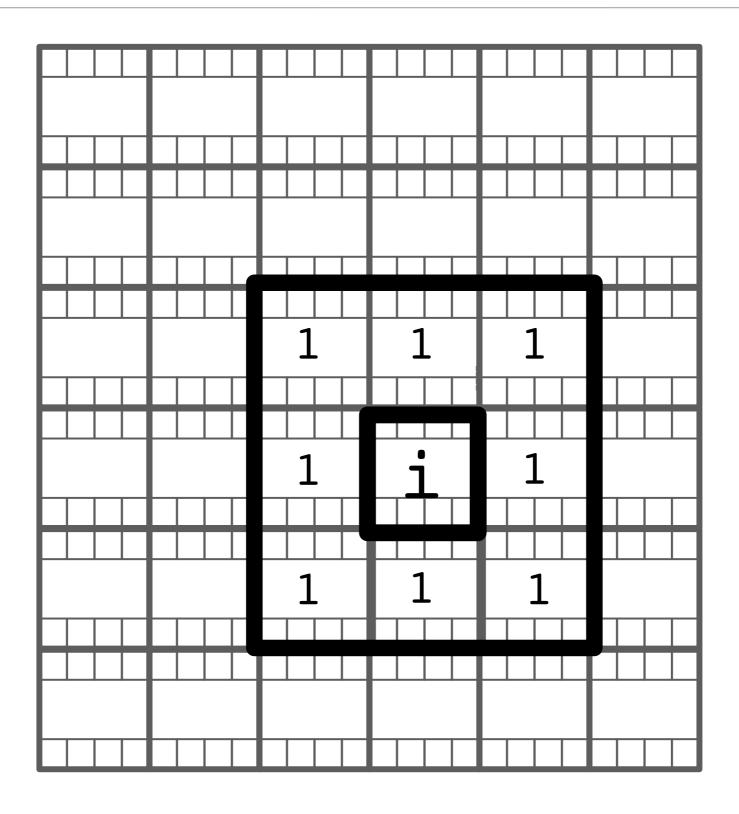

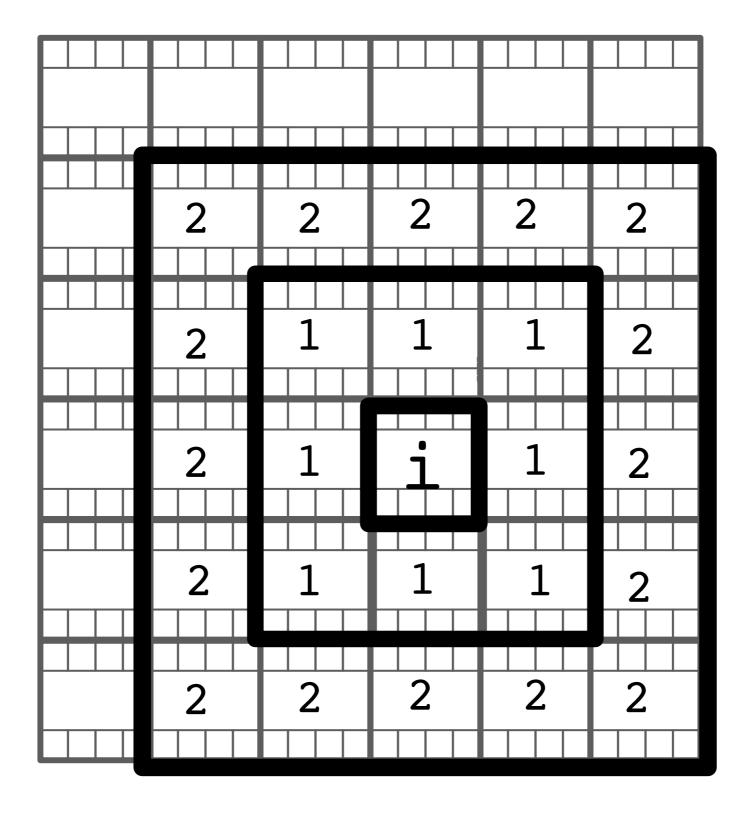

- Assignment in units of multiples of clusters called Ensembles

- Simple, clustered hardware to exploit within-die variation

- Each cluster supports a different max f at chip-wide, single Vdd

- Cluster selection mimics multi-Vdd adaptation

- Assignment in units of multiples of clusters called Ensembles

- Each ensemble constitutes a f domain

- Simple, clustered hardware to exploit within-die variation

- Each cluster supports a different max f at chip-wide, single Vdd

- Cluster selection mimics multi-Vdd adaptation

- Assignment in units of multiples of clusters called Ensembles

- Each ensemble constitutes a f domain

- Each ensemble cycles at the f of slowest component cluster

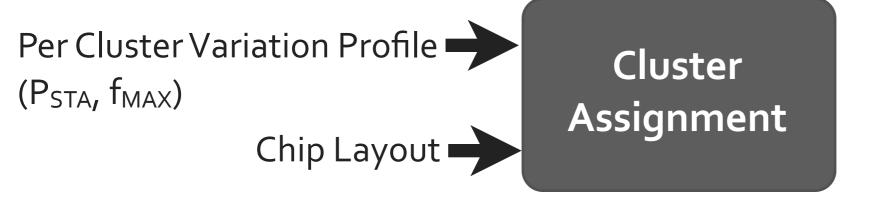

Goal: Maximize MIPS/Watt subject to

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

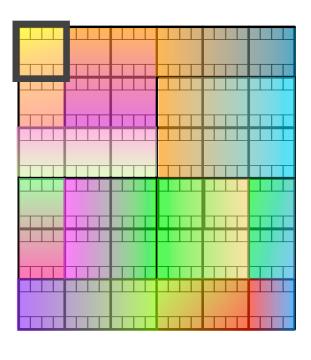

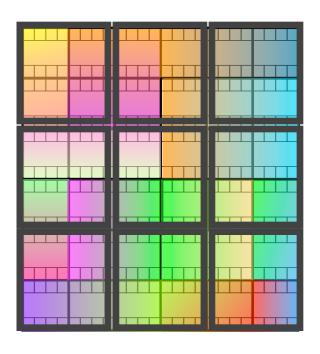

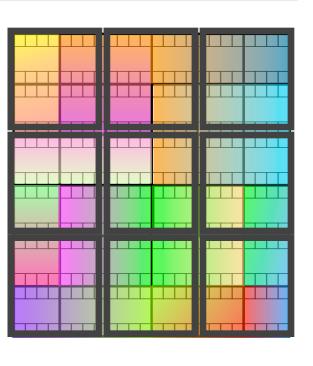

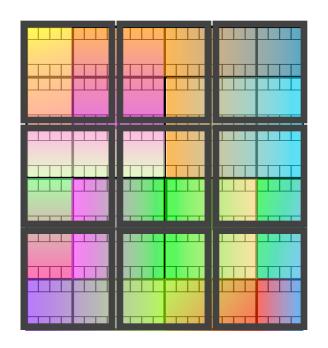

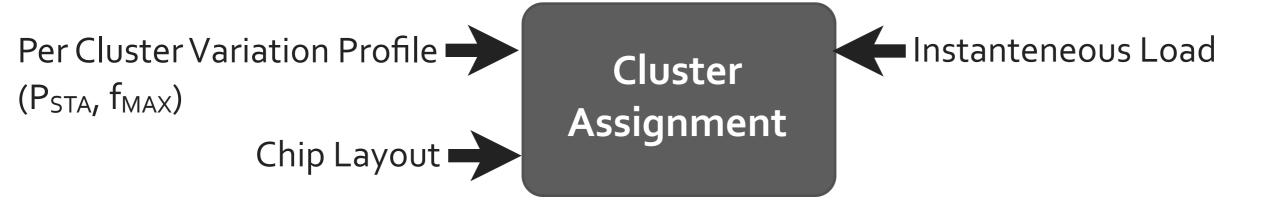

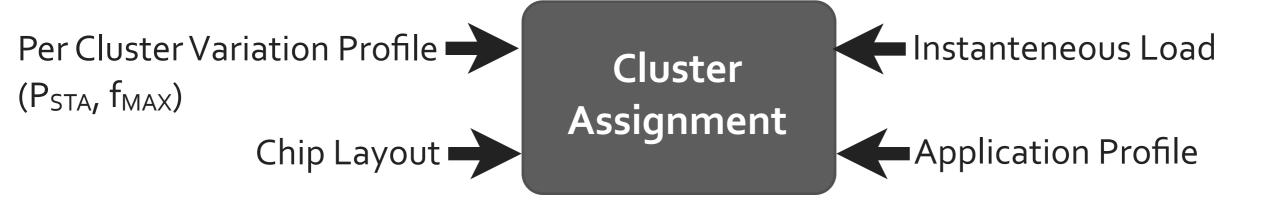

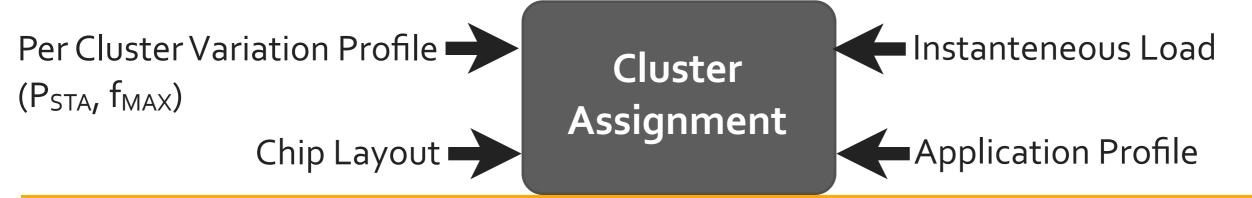

Per Cluster Variation Profile  $(P_{STA}, f_{MAX})$

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

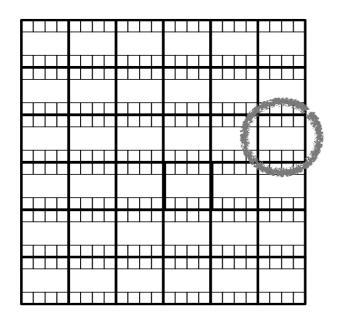

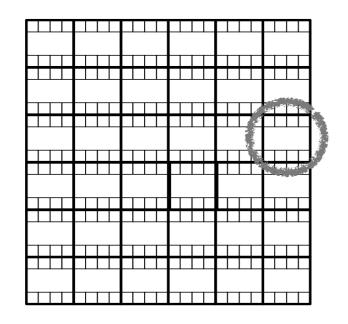

# Cluster Assignment

- Goal: Maximize MIPS/Watt subject to

- Power budget and maximum temperature

- Distance between allocated clusters

**Simple**

Single Vdd value

Assignment at cluster granularity

Single f per ensemble

| 1  | 2  | 3  | 4  | 5  | 6  |

|----|----|----|----|----|----|

|    |    |    |    |    |    |

| 7  | 8  | 9  | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 |

| 31 | 32 | 33 | 34 | 35 | 36 |

|      | $\Box$ |    | 1   |    |    |

|------|--------|----|-----|----|----|

| 1    | 2      | 3  | 4   | 5  | 6  |

|      |        |    |     |    |    |

| 7    | 8      | 9  | 10  | 11 | 12 |

|      |        |    |     |    |    |

| 13   | 14     | 15 | 16  | 17 | 18 |

|      |        |    | +++ |    |    |

| 19   | 20     | 21 | 22  | 23 | 24 |

|      | +++    |    |     |    |    |

| 25   | 26     | 27 | 28  | 29 | 30 |

| ┠┼┼┼ |        |    |     |    |    |

| 31   | 32     | 33 | 34  | 35 | 36 |

|      |        |    |     |    |    |

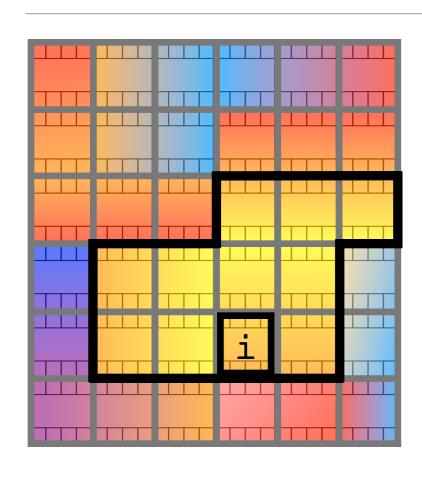

$f_A = min(f_8, f_9, f_{14}, f_{15})$

| 1      | 2  | 3  | 4  | 5  | 6  |

|--------|----|----|----|----|----|

|        |    |    |    |    |    |

| 7<br>  | 8  | 9  | 10 | 11 | 12 |

| 13     | 14 | 15 | 16 | 17 | 18 |

| 19     | 20 | 21 | 22 | 23 | 24 |

| 25<br> | 26 | 27 | 28 | 29 | 30 |

| 31     | 32 | 33 | 34 | 35 | 36 |

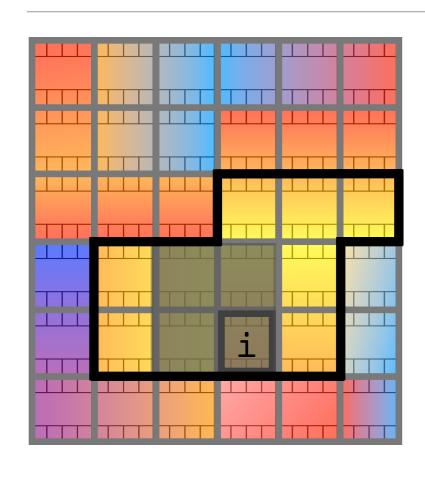

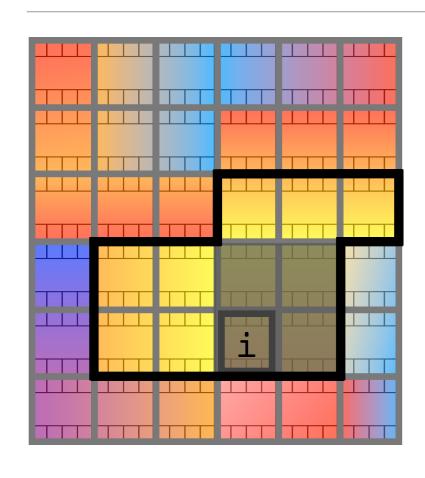

$$f_A = min(f_8, f_9, f_{14}, f_{15})$$

$$f_B = min(f_{5}, f_{6}, f_{11}, f_{12}, f_{17}, f_{18}, f_{23}, f_{24})$$

|                |     |    |          | -  |    |

|----------------|-----|----|----------|----|----|

|                |     |    |          |    |    |

| 1              | 2   | 3  | 4        | 5  | 6  |

| _ <del>-</del> |     |    | <u> </u> |    |    |

|                |     |    |          |    |    |

|                |     |    |          |    |    |

| 7              | 8   | 9  | 10       | 11 | 12 |

|                |     |    |          |    |    |

|                |     |    | +++      |    |    |

| 13             | 14  | 15 | 16       | 17 | 18 |

| 12             | T 4 | 13 | 10       | Τ/ | TO |

|                |     |    |          |    |    |

|                |     |    |          |    |    |

| 19             | 20  | 21 | 22       | 23 | 24 |

|                |     |    |          |    |    |

|                |     |    |          |    |    |

|                | 26  | 27 |          |    | 20 |

| 25             | 26  | 27 | 28       | 29 | 30 |

|                |     |    |          |    |    |

|                |     |    |          |    |    |

| 31             | 32  | 33 | 34       | 35 | 36 |

|                | 32  | 33 |          |    |    |

|                |     |    |          |    |    |

$$f_A = \min(f_{8}, f_{9}, f_{14}, f_{15})$$

$$f_B = min(f_5, f_6, f_{11}, f_{12}, f_{17}, f_{18}, f_{23}, f_{24})$$

$$f_C = min(f_{20}, f_{26}, f_{27}, f_{28}, f_{29}, f_{30}, f_{32}, f_{33})$$

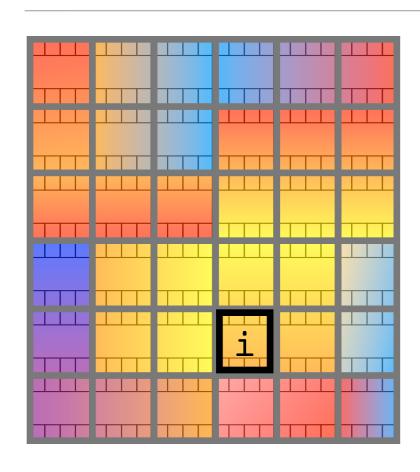

A task demands N = |E| clusters

For each available cluster i

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{array}{c} \text{MIPS} \\ \text{Watt} \\ \text{max}_{\text{E}} & \text{IPC}(f_{\text{E}}) \times |\text{E}| \times f_{\text{E}} \\ \text{Watt} \\ \end{array}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} & \underset{\text{maxe}}{\text{maxe}} \frac{\text{MIPS}}{\text{Watt}} \\ & \underset{\text{maxe}}{\text{IPC(f_E)}} \times |\text{E}| \times \text{f_E} \\ & \\ & \sum_{E} \text{P_{STA}} + \sum_{E} \text{P_{DYN}} \end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} & \underset{\text{maxe}}{\text{maxe}} \frac{\text{MIPS}}{\text{Watt}} \\ & \underset{\text{maxe}}{\text{IPC(f_E)}} \times |E| \times f_E \\ & \frac{\sum_{E} P_{STA} + C \times Vdd^2 \times |E| \times f_E}{\end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} & \underset{\text{maxe}}{\text{maxe}} \frac{\text{MIPS}}{\text{Watt}} \\ & \underset{\text{maxe}}{\text{IPC(f_E)}} \times \frac{|\textbf{E}|}{\text{x f_E}} \times \text{f_E} \\ & \underset{\text{E}|}{\sum_{E} P_{STA}} + C \times \text{Vdd}^2 \times \frac{|\textbf{E}|}{\text{x f_E}} \end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} & \underset{\text{maxe}}{\text{maxe}} \frac{\text{MIPS}}{\text{Watt}} \\ & \underset{\text{maxe}}{\text{IPC(f_E)}} \times \frac{|\textbf{E}|}{\text{x f_E}} \times \text{f_E} \end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} & \underset{\text{maxe}}{\text{maxe}} \frac{\text{MIPS}}{\text{Watt}} \\ & \underset{\text{maxe}}{\text{IPC(f_E)}} \times \frac{|\textbf{E}|}{\text{x f_E}} \times \text{f_E} \\ & \sum_{E} P_{STA} + \textbf{C} \times \text{Vdd}^2 \times \frac{|\textbf{E}|}{\text{x f_E}} \times \text{f_E} \end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} & \underset{\text{maxe}}{\text{maxe}} \frac{\text{MIPS}}{\text{Watt}} \\ & \underset{\text{maxe}}{\text{IPC(f_E)}} \times \frac{|\textbf{E}|}{\text{x}} \times \frac{|\textbf{f_E}|}{\text{f_E}} \\ & \sum_{E} P_{STA} + \textbf{C} \times \text{Vdd}^2 \times \frac{|\textbf{E}|}{\text{x}} \times \frac{|\textbf{f_E}|}{\text{f_E}} \end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} & \underset{\text{maxe}}{\text{maxe}} \frac{\text{MIPS}}{\text{Watt}} \\ & \underset{\text{maxe}}{\text{IPC(fe)}} \times |\textbf{E}| \times \textbf{fe} \\ & \sum_{E} P_{STA} + \textbf{C} \times \textbf{Vdd}^2 \times |\textbf{E}| \times \textbf{fe} \end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

$$\begin{aligned} \text{max}_{E} & \xrightarrow{\text{MIPS}} \\ & \text{Watt} \\ & \text{max}_{E} & \xrightarrow{\text{IPC(f_E)} \times |E| \times f_{E}} \\ & \sum_{E} P_{STA} + C \times Vdd^{2} \times |E| \times f_{E} \\ & \equiv \min_{E} \sum_{E} P_{STA} \end{aligned}$$

- For each available cluster i

- Enumerate all ensembles E where the cluster i is slowest

- Ensemble frequency  $f_E = f_i$

- Consider only clusters of higher f<sub>MAX</sub>

- Pick the ensemble max<sub>E</sub> MIPS/Watt

- ▶ Linear-complexity operation if clusters are sorted offline

$$\frac{|PC(f_E) \times |E| \times f_E}{\sum_{E} P_{STA} + C \times Vdd^2 \times |E| \times f_E}$$

$$\equiv min_E \, \sum_E P_{STA}$$

✓ Simple clustered hardware architecture

- √ Simple clustered hardware architecture

- √ Tolerates variation with a single physical Vdd domain

- √ Simple clustered hardware architecture

- √ Tolerates variation with a single physical Vdd domain

- Cluster selection replaces multi-Vdd adaptation

- √ Simple clustered hardware architecture

- √ Tolerates variation with a single physical Vdd domain

- Cluster selection replaces multi-Vdd adaptation

- √ Simple cluster assignment

- √ Simple clustered hardware architecture

- √ Tolerates variation with a single physical Vdd domain

- Cluster selection replaces multi-Vdd adaptation

- √ Simple cluster assignment

- Needs cluster profiling

# **Evaluation Setup**

# **Evaluation Setup**

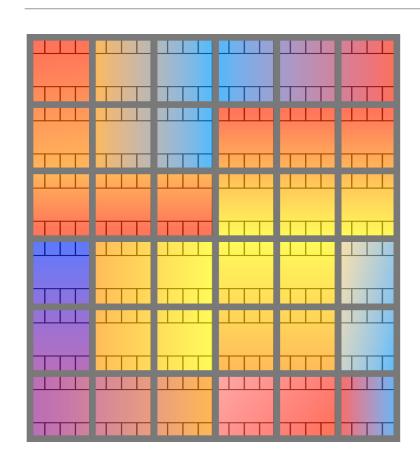

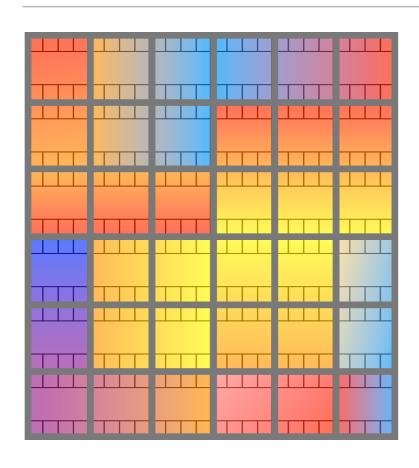

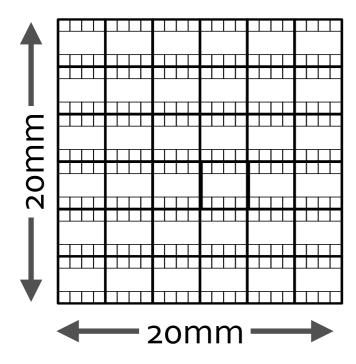

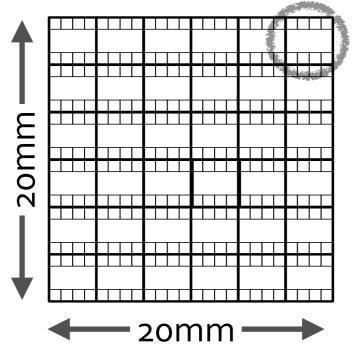

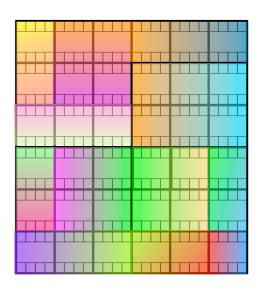

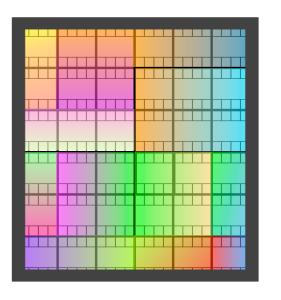

• Simulated 288 core chip at 11nm:

- Simulated 288 core chip at 11nm:

- 36 clusters, 8 cores per cluster

- Simulated 288 core chip at 11nm:

- 36 clusters, 8 cores per cluster

- Core: Single issue in-order

Core + Local Memory

- Simulated 288 core chip at 11nm:

- 36 clusters, 8 cores per cluster

- Core: Single issue in-order

- VARIUS-NTV model to find the per-cluster min Vdd and max f

Core + Local Memory

- Simulated 288 core chip at 11nm:

- 36 clusters, 8 cores per cluster

- Core: Single issue in-order

- VARIUS-NTV model to find the per-cluster min Vdd and max f

- Multi-programmed workload based on PARSEC

Core + Local Memory

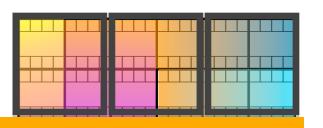

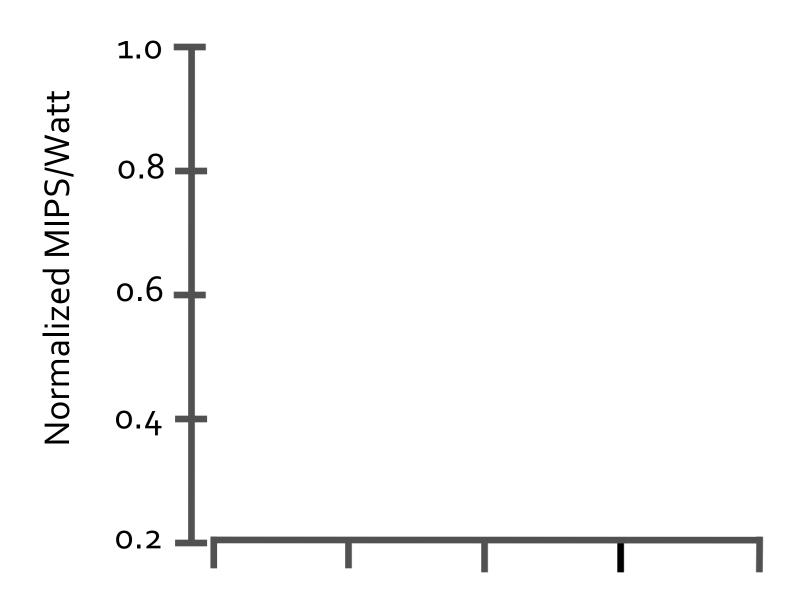

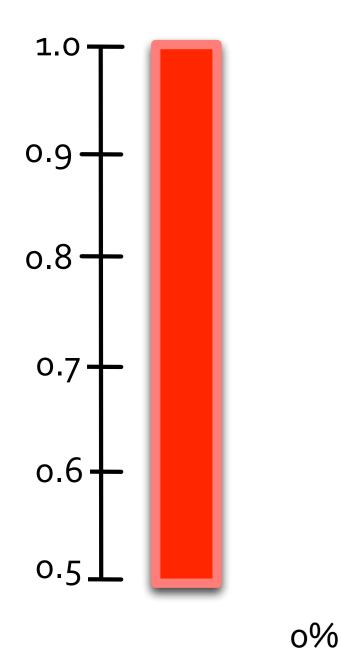

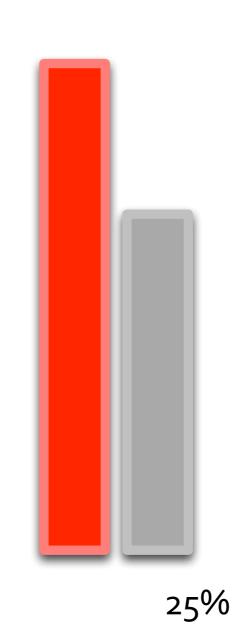

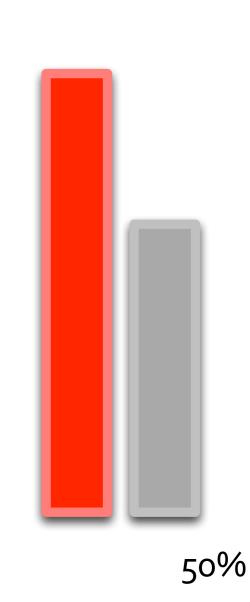

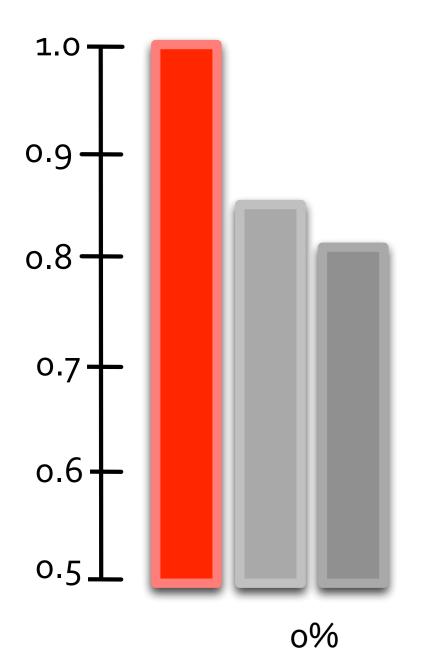

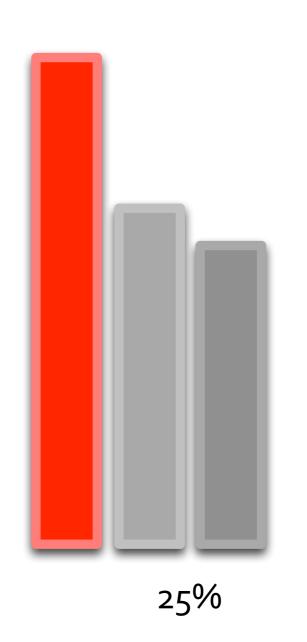

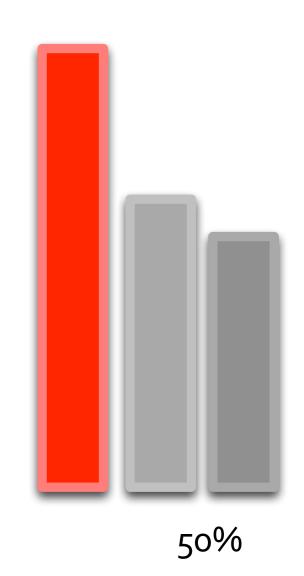

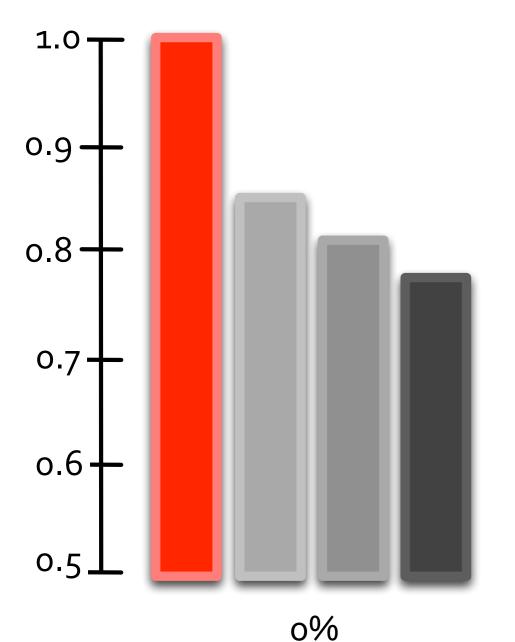

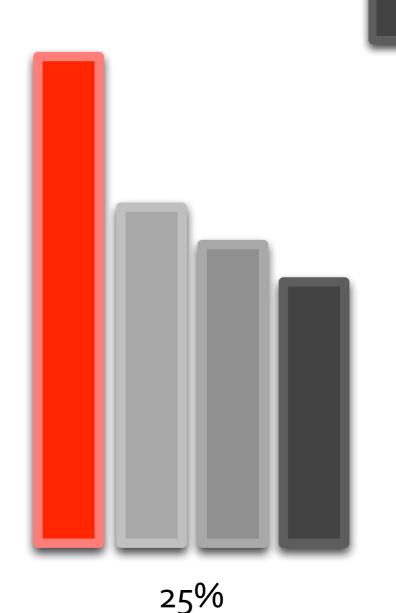

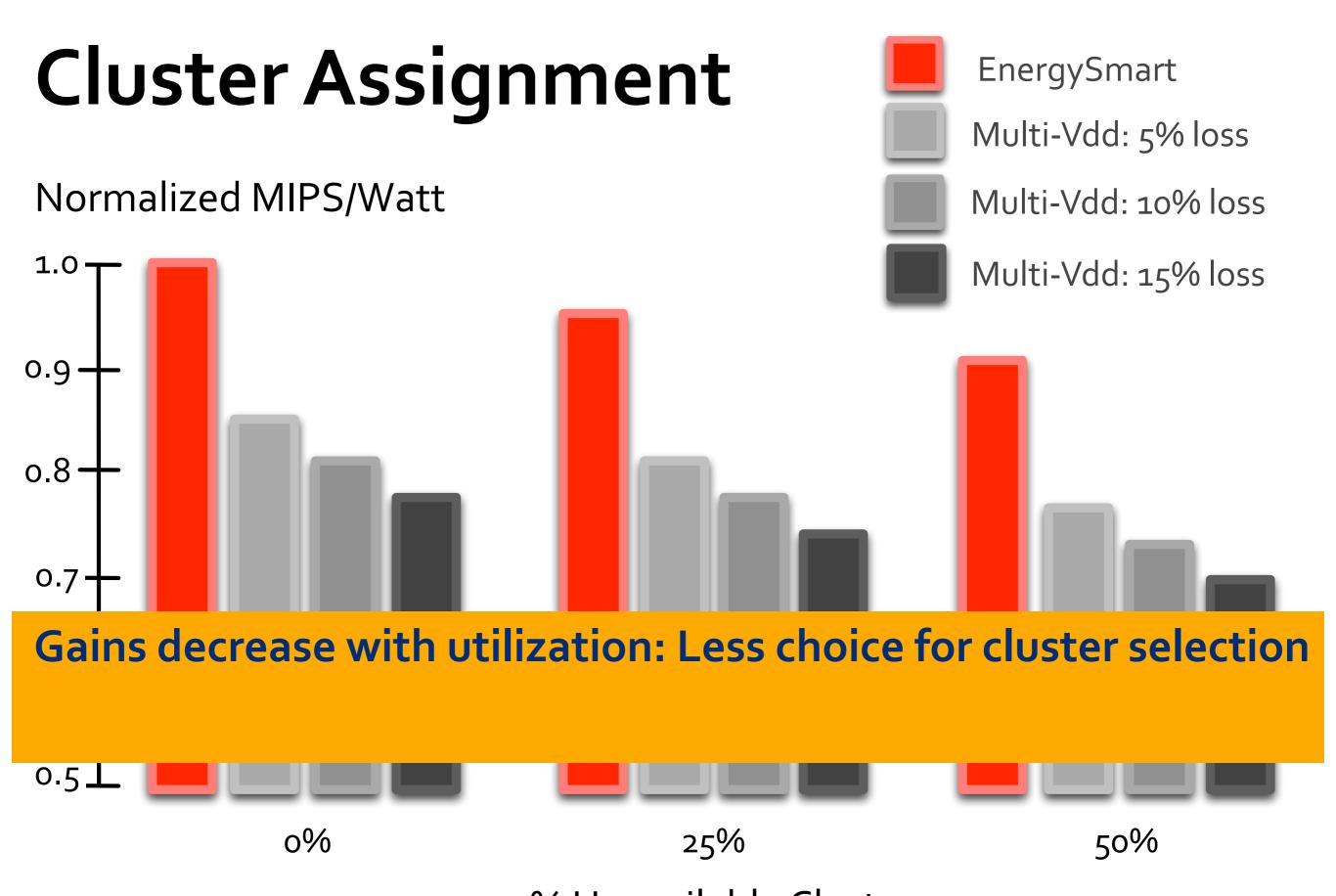

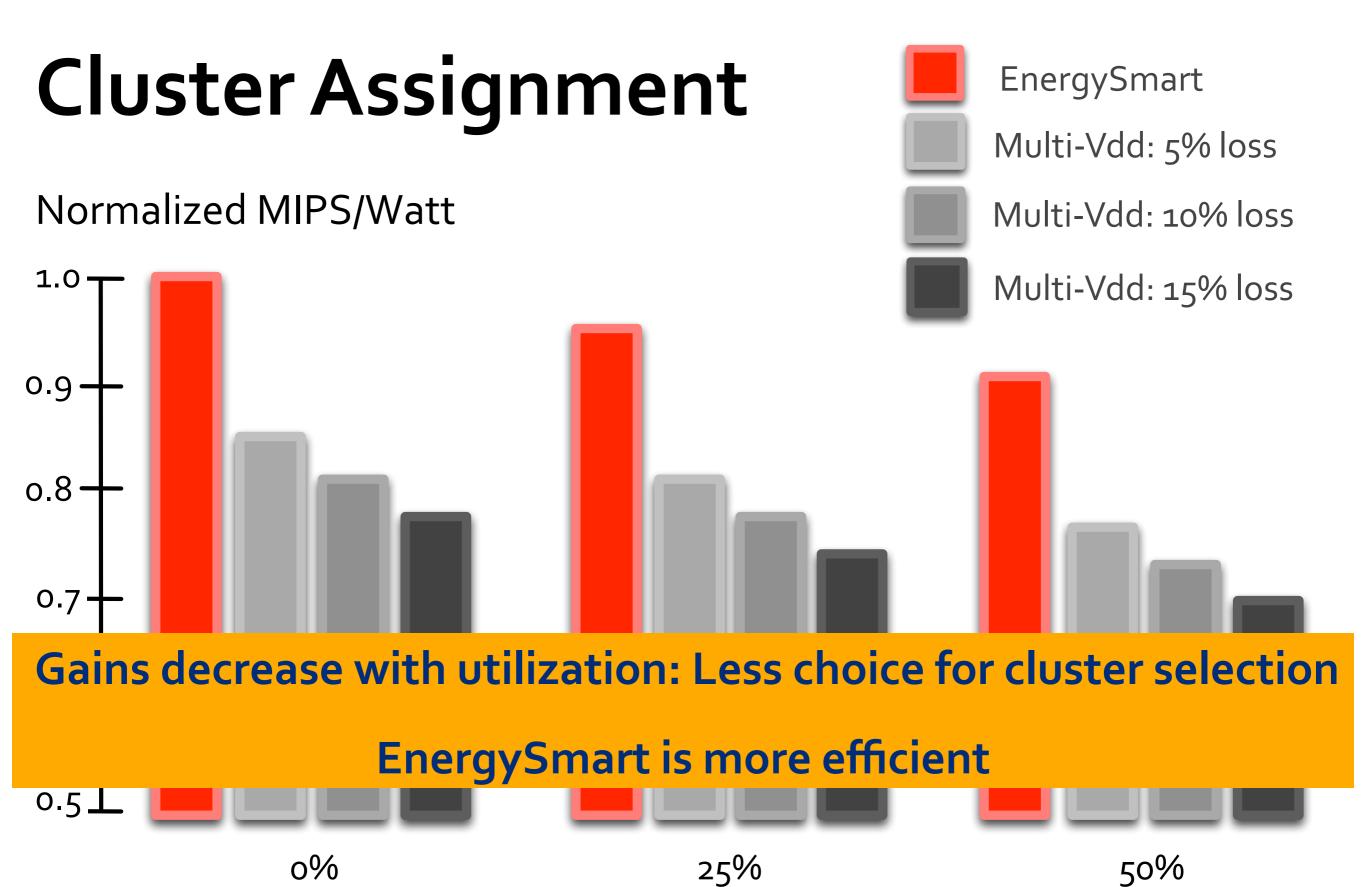

**EnergySmart is more efficient**

Normalized MIPS/Watt

0% 25% 50%

Normalized MIPS/Watt

25%

% Unavailable Clusters

EnergySmart

50%

Normalized MIPS/Watt

% Unavailable Clusters

Normalized MIPS/Watt

Multi-Vdd: 10% loss

% Unavailable Clusters

Normalized MIPS/Watt

EnergySmart

Multi-Vdd: 5% loss

Multi-Vdd: 10% loss

Multi-Vdd: 15% loss

% Unavailable Clusters

% Unavailable Clusters

**Energy Smart:**

**Energy Smart:**

#### **Energy Smart:**

Eschewing multi-Vdd domains to tolerate variation at NTV

Multiple f domains rather than Vdd domains

#### **Energy Smart:**

- Multiple f domains rather than Vdd domains

- Cluster selection replaces multi-Vdd adaptation

#### **Energy Smart:**

- Multiple f domains rather than Vdd domains

- Cluster selection replaces multi-Vdd adaptation

- Simple clustered hardware architecture

#### **Energy Smart:**

- Multiple f domains rather than Vdd domains

- Cluster selection replaces multi-Vdd adaptation

- Simple clustered hardware architecture

- Simple, variation-aware cluster assignment

#### **Energy Smart:**

- Multiple f domains rather than Vdd domains

- Cluster selection replaces multi-Vdd adaptation

- Simple clustered hardware architecture

- Simple, variation-aware cluster assignment

- Energy-efficiency within 81% of perfect organization

#### **Energy Smart:**

- Multiple f domains rather than Vdd domains

- Cluster selection replaces multi-Vdd adaptation

- Simple clustered hardware architecture

- Simple, variation-aware cluster assignment

- Energy-efficiency within 81% of perfect organization

- Realistic multi-Vdd organization achieves only 69% (at 90% regulator efficiency)

# EnergySmart: Toward Energy Efficient Many Co

# Toward Energy-Efficient Many-Cores for Near-Threshold Voltage Computing

Ulya R. Karpuzcu\*, Abhishek Sinkar\*, Nam Sung Kim\*, Josep Torrellas\*

\*University of Minnesota \*University of Illinois \*University of Wisconsin

University of Minnesota